Tab:835-12

rev:B3

Number: AiP31565CR-AX-XS-A040EN

## **Product** Specification

#### **Specification Revision History:**

| Version    | Date    | Description                                     |

|------------|---------|-------------------------------------------------|

| 2019-03-A1 | 2019-03 | New                                             |

| 2019-12-B1 | 2019-12 | Replace the new template and modify the content |

|            |         |                                                 |

|            |         |                                                 |

Address: Building B4,NO.777,Jianzhu Road,Binhu District,Wuxi City,Jiangsu Province 1/ 49 http://www.i-core. cn P.C.: 214072 VER:2019-12-B1

Tab:835-12 rev:B3

Number: AiP31565CR-AX-XS-A040EN

#### 1. General Description

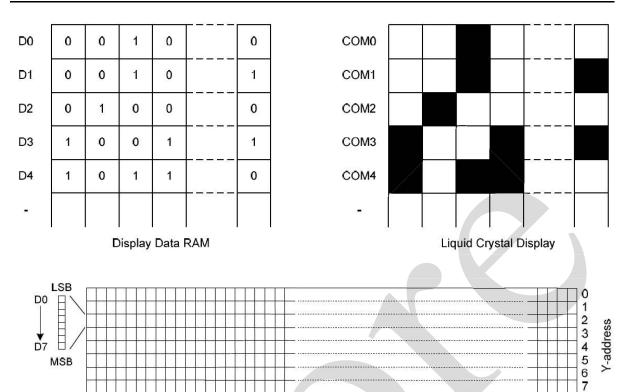

The AiP31565CR is a single-chip dot matrix LCD driver that can be connected directly to a microprocessor bus. 8-bit parallel or 4-line SPI display data sent from the microprocessor is stored in the internal display data RAM and the chip generates a LCD drive signal independent of the microprocessor. Because the chips in the AiP31565CR contain 65×132 bits of display data RAM and there is a 1-to-1 correspondence between the LCD panel pixels and the internal RAM bits, these chips enable displays with a high degree of freedom.

The AiP31565CR chips contain 65 common output circuits and 132 segment output circuits, so that a single chip can drive a 65×132 dot display (capable of displaying 8 columns×4 rows of a 16×16 dot kanji font).

The chips are able to minimize power consumption because no external operating clock is necessary for the display data RAM read/write operation. Furthermore, because each chip is equipped internally with a low-power LCD driver power supply, resistors for LCD driver power voltage adjustment and a display clock CR oscillator circuit, the AiP31565CR can be used to create the lowest power display system with the fewest components for high-performance portable devices.

#### **Features:**

- Directly display RAM data through Display Data RAM.

- RAM capacity:65×132=8580 bits

- Display duty selectable by select pin

1/65 duty:65 common×132 segment

1/49 duty:49 common×132 segment

1/33 duty:33 common×132 segment

1/55 duty:55 common×132 segment

1/53 duty:53 common×132 segment

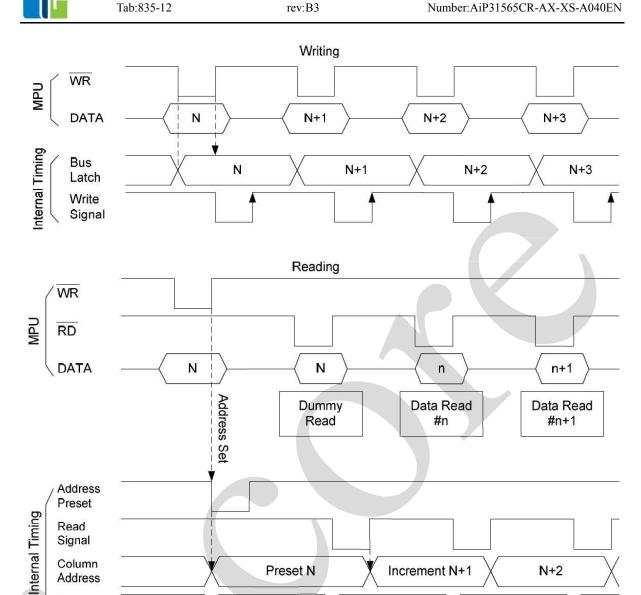

- Bidirectional 8-bit parallel interface supports: 8080-series and 6800-series MPU

Serial interface (SPI-4) is also supported (write only)

- Abundant command functions

Display data Read/Write, display ON/OFF, Normal/Reverse display mode, page address set, display start line set, column address set, status read, display all points ON/OFF, LCD bias set, electronic volume, read/modify/write, segment driver direction selects, power saver, common output status select, V0 voltage regulation internal resistor ratio set.

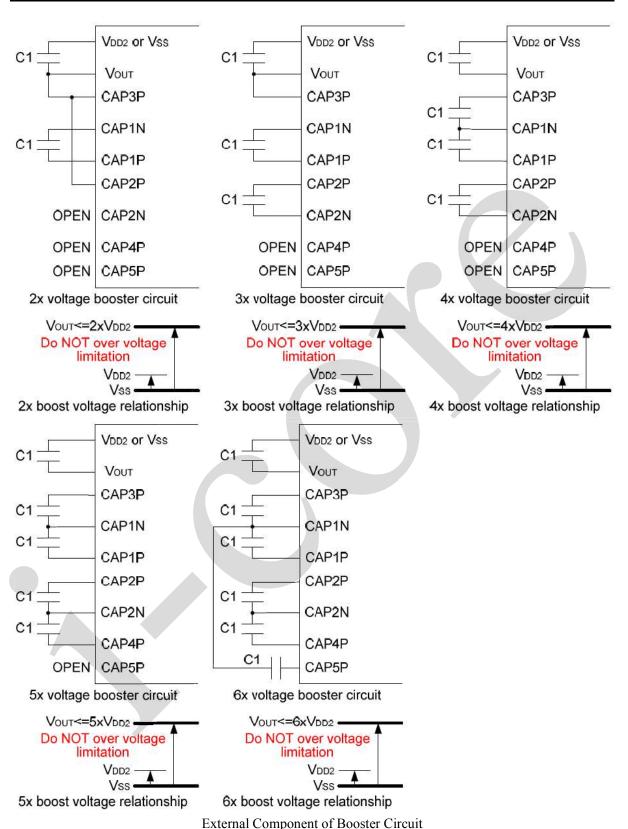

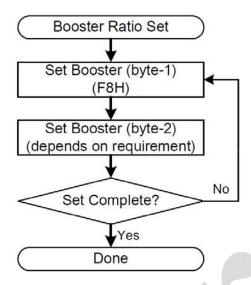

- Embedded analog power supply circuits for Liquid Crystal driving: Booster, Regulator and Follower.

- Embedded Booster circuit:

$2\times,3\times,4\times,5\times$  and  $6\times$  boost ratios are supported. Independent input (VDD2) for boost reference voltage.

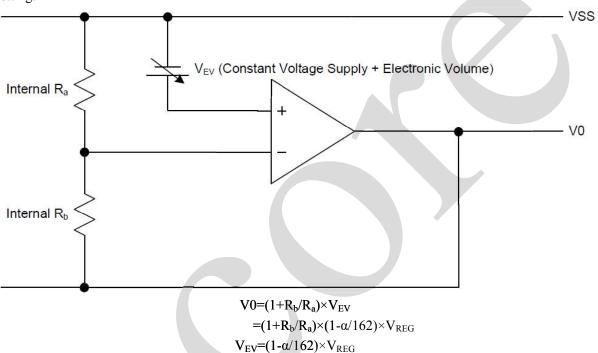

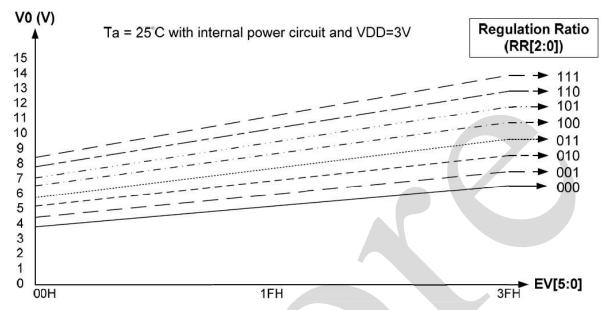

High-accuracy Regulator circuit:

Build-in Electronic volume function for the contrast control. Thermal gradient=-0.05%/°C.

Tab:835-12 rev:B3 Number:AiP31565CR-AX-XS-A040EN

- Embedded voltage Follower circuit for LCD driving.

- Embedded R-C oscillator circuit.

The external clock is also supported.

• Extremely low power consumption:60uA, bare dice (using the internal power).

#### Settings:

VDD-VSS=VDD2-VSS=3.0V,Booster Ratio=4, V0-VSS=11.0V. Display OFF and the normal mode is selected.

• Logic power supply: VDD-VSS=2.4V to 3.3V

Analog Power (Boost reference voltage):

VDD2-VSS=2.4V to 3.3V

Booster maximum voltage limited

VOUT=13.5V

Liquid crystal drive power supply:V0–VSS=3.0V to 12.0V

- Wide range of operating temperatures:–30 to 80°C

- Package type:COG only.

- The chip is not designed to resist the light or to resist the radiation.

Address: Building B4,NO.777,Jianzhu Road,Binhu District,Wuxi City,Jiangsu Province

http://www.i-core. cn

P.C.: 214072

VER:2019-12-B1

ab:835-12 rev:B3

Number: AiP31565CR-AX-XS-A040EN

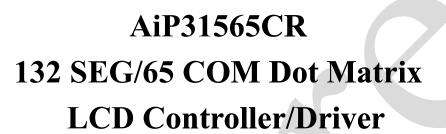

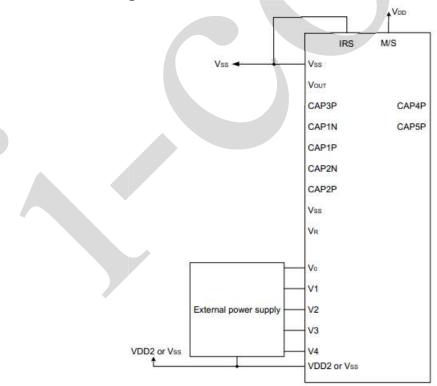

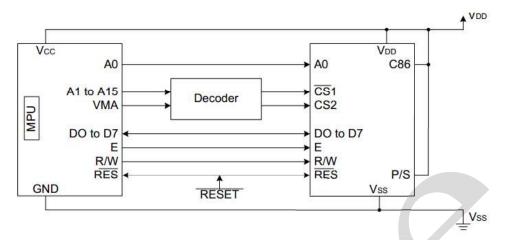

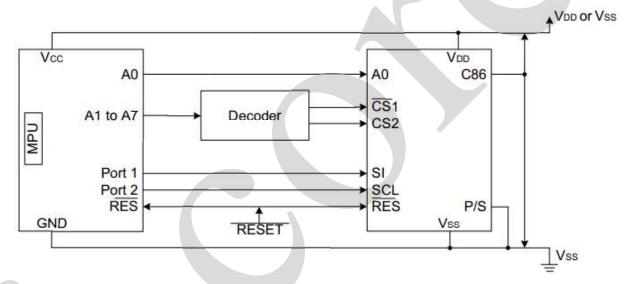

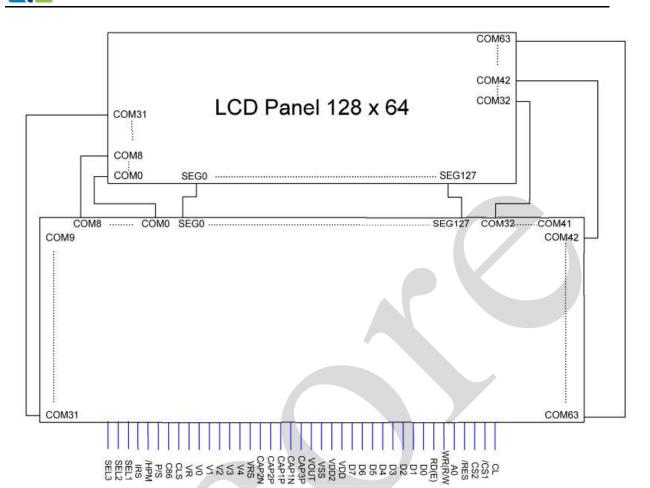

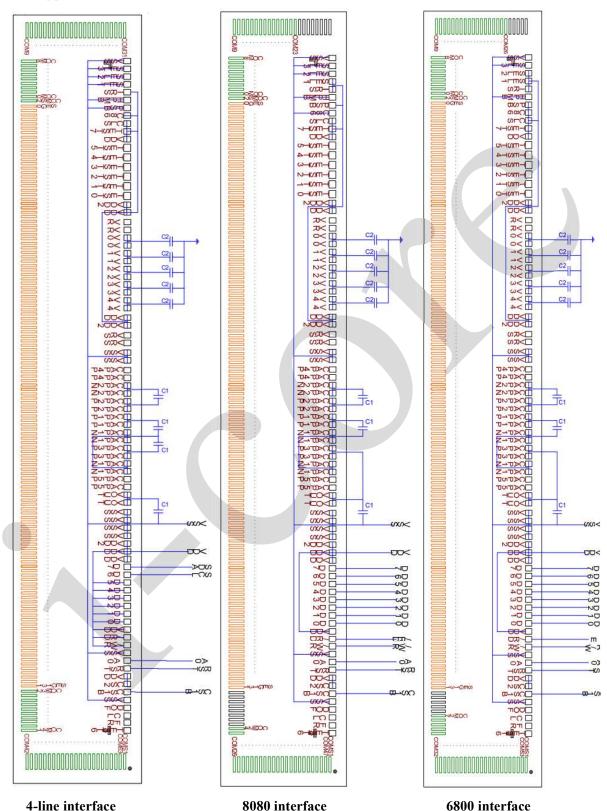

#### 2, Block Diagram And PAD Description

#### 2.1, Block Diagram

Address: Building B4,NO.777,Jianzhu Road,Binhu District,Wuxi City,Jiangsu Province 4/ 49 http://www.i-core. cn P.C.: 214072 VER:2019-12-B1

# Wuxi I-CORE Electronics Co., Ltd. ab:835-12 rev:B3 Number:AiP31565CR-AX-XS-A040EN

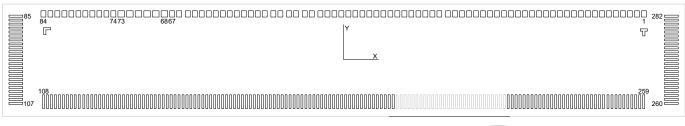

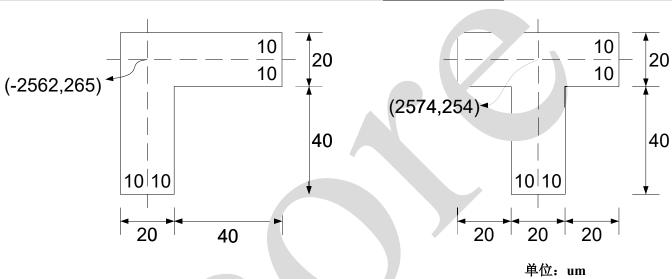

### 2.2, PAD Description

| PAD No.          | PAD   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Description          |                    |                   |  |  |

|------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------|-------------------|--|--|

| I IDD            | Name  | D 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <u> </u>             |                    |                   |  |  |

| VDD              | Power | Power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      |                    |                   |  |  |

| VDD2             | Power | Power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      |                    |                   |  |  |

| VSS              | Power | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1 0 4 10             | D 1                | 1, 1,             |  |  |

| VRS              | Power | This is the internal-ou                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | tput V <sub>REG</sub> power s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | upply for the LC     | D power supply v   | oltage regulator. |  |  |

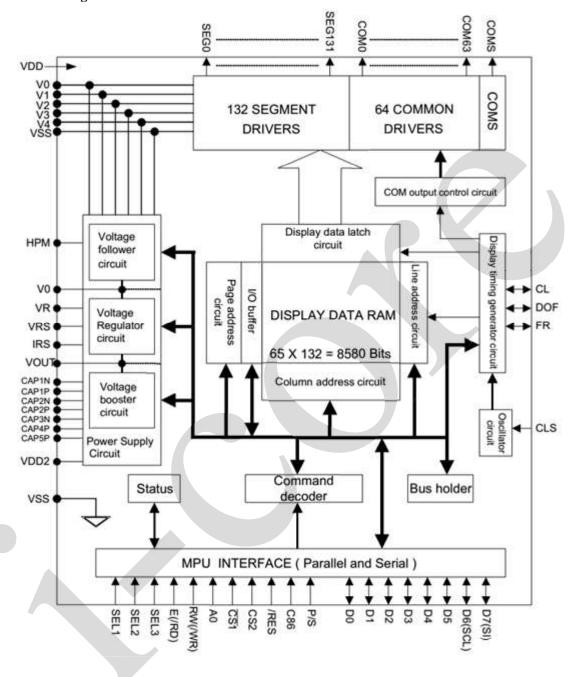

| V0、V1<br>V2、V3   | Power | is determined by the lidivided or through determined based on V V0≥V1≥V2≥V3≥V4≥ When the power supp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | his is a multi-level power supply for the liquid crystal drive. The voltage Supply applied determined by the liquid crystal cell, and is changed through the use of a resistive voltage vided or through changing the impedance using an op. amp. Voltage levels are termined based on VSS, and must maintain the relative magnitudes shown below.  10 \( \frac{1}{2}\text{V2}\text{V3}\( \frac{1}{2}\text{V4}\( \frac{1}{2}\text{VSS} \)  11 The the power supply turns ON, the internal power supply circuits produce the V1 to Voltages shown below. The voltage settings are selected using the LCD bias set command. |                      |                    |                   |  |  |

| V4               |       | 1/65 Duty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1/49 Duty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1/33 Duty            | 1/55 Duty          | 1/53 Duty         |  |  |

|                  |       | V1 8/9V0,6/7V0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7/8V0,5/6V0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5/6V0,4/5V0          | 7/8V0,5/6V0        | 7/8V0,5/6V0       |  |  |

|                  |       | V2 7/9V0,5/7V0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6/8V0,4/6V0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4/6V0,3/5V0          | 6/8V0,4/6V0        | 6/8V0,4/6V0       |  |  |

|                  |       | V3 2/9V0,2/7V0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2/8V0,2/6V0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2/6V0,2/5V0          | 2/8V0,2/6V0        | 2/8V0,2/6V0       |  |  |

|                  |       | V4 1/9V0,1/7V0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1/8V0,1/6V0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1/6V0,1/5V0          | 1/8V0,1/6V0        | 1/8V0,1/6V0       |  |  |

|                  |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      | ,                  |                   |  |  |

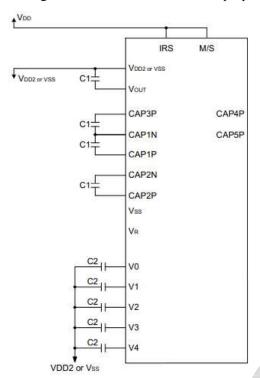

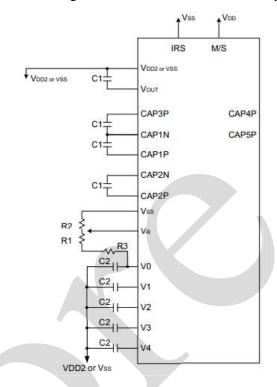

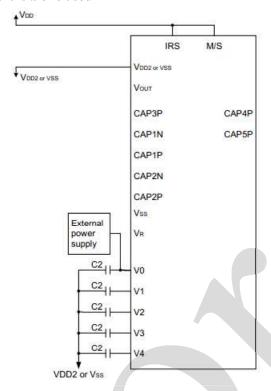

| CAP1P            | О     | DC/DC voltage conv terminal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | erter. Connect a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | capacitor between    | en this terminal   | and the CAP1N     |  |  |

| CAP1N            | О     | DC/DC voltage conv terminal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | erter. Connect a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | capacitor betwee     | en this terminal   | and the CAP1P     |  |  |

| CAP2P            | О     | DC/DC voltage conv terminal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | erter. Connect a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | capacitor between    | en this terminal   | and the CAP2N     |  |  |

| CAP2N            | О     | DC/DC voltage conv terminal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | erter. Connect a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | capacitor betwe      | en this terminal   | and the CAP2P     |  |  |

| CAP3P            | 0     | DC/DC voltage conv terminal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | erter. Connect a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | capacitor between    | en this terminal   | and the CAP1N     |  |  |

| CAP4P            | О     | DC/DC voltage conv terminal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | erter. Connect a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | capacitor between    | en this terminal   | and the CAP2N     |  |  |

| CAP5P            | О     | DC/DC voltage conv terminal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | erter. Connect a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | capacitor between    | en this terminal   | and the CAP1N     |  |  |

| VOUT             | 0     | DC/DC voltage conveterminal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | erter. Connect a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | capacitor between    | n this terminal a  | nd VSS or VDD     |  |  |

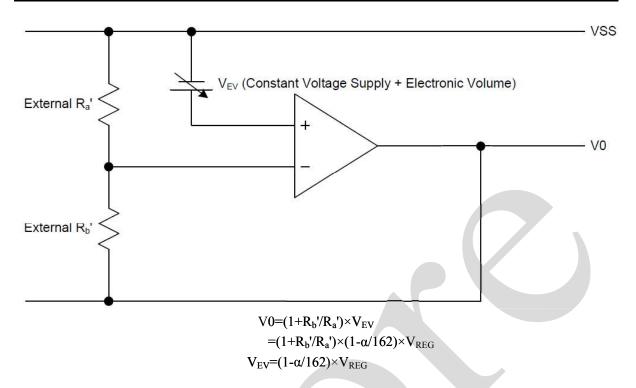

| VR               | I     | Output voltage regularesistive voltage divided IRS="L":the V0 voltaged IRS="H":the V0 voltaged IRS="H" | er.<br>ge regulator interr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | nal resistors are no | ot used.           | nd V0 through a   |  |  |

| D5~D0<br>D6(SCL) | I/O   | This is an 8-bit bi-dire bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ctional data bus tl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | nat connects to an   | 8-bit or 16-bit st | andard MPU data   |  |  |

Address: Building B4,NO.777,Jianzhu Road,Binhu District,Wuxi City,Jiangsu Province 5/49 http://www.i-core. cn P.C.: 214072 VER:2019-12-B1

# Wuxi I-CORE Electronics Co., Ltd. Tab:835-12 rev:B3 Number:AiP31565CR-AX-XS-A040EN

|        | 1ab:835 | -12         | rev:B3                    |                                  | Number: AIP31363CR     | -AX-XS-AU4UEN          |        |

|--------|---------|-------------|---------------------------|----------------------------------|------------------------|------------------------|--------|

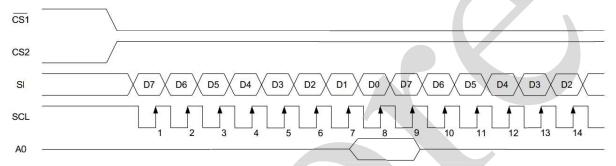

| D7(SI) |         | When the    | serial interface (SPI-4   | ) is selected (P                 | /S="L"):               |                        |        |

|        |         | D7 : seria  | l data input (SI);D6:th   | e serial clock in                | nput (SCL).            |                        |        |

|        |         | D0 to D5    | should be connected to    | o VDD or float                   | ing.                   |                        |        |

|        |         | When the    | chip select is not activ  | e, D0 to D7 ar                   | e set to high impeda   | nce.                   |        |

|        |         | This is co  | nnect to the least signi  | ficant bit of the                | e normal MPU addre     | ess bus, and it deterr | nines  |

| A0     | I       | whether th  | ne data bits are data or  | command.                         |                        |                        |        |

| Au     | 1       | A0="H":I    | indicates that D0 to D7   | are display da                   | ta.                    |                        |        |

|        |         | A0="L":I    | ndicates that D0 to D7    | are control da                   | ta.                    |                        |        |

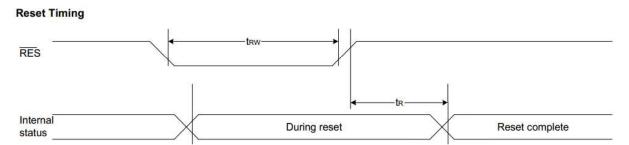

| /RES   | I       | When /RE    | ES is set to "L", the reg | gister settings a                | re initialized (cleare | d).                    |        |

| /KES   | 1       | The reset   | operation is performed    | d by the /RES s                  | ignal level.           |                        |        |

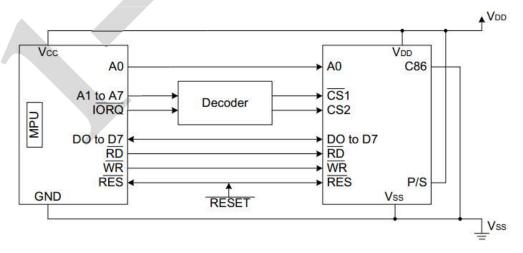

| CS1    | ı       | This is the | e chip select signal. W   | Then $\overline{\text{CS1}}$ ="L | "and CS2="H",then      | the chip select bec    | omes   |

| CS2    | I       |             | d data/command I/O is     |                                  |                        |                        |        |

|        |         | -           | onnected to 8080 serie    |                                  | in is treated as the ' | '/RD" signal of the    | 8080   |

| /RD    |         |             | is LOW-active. The d      |                                  |                        |                        |        |

| (E)    | I       | • When c    | onnected to 6800 seri     | es MPU, this                     | pin is treated as the  | e "E" signal of the    | 6800   |

|        |         |             | is HIGH-active. This      |                                  |                        |                        |        |

|        |         | • When co   | onnected to 8080 serie    | es MPU, this p                   | in is treated as the " | /WR" signal of the     | 8080   |

| /11/10 |         | MPU and     | is LOW-active. The s      | signals on the                   | data bus are latched   | at the rising edge of  | of the |

| /WR    | I       | /WR signa   | al.                       |                                  |                        |                        |        |

| (R/W)  |         | • When co   | onnected to 6800 series   | es MPU, this p                   | in is treated as the " | R/W" signal of the     | 6800   |

|        |         | MPU and     | decides the access typ    | e:When R/W=                      | "H":Read.When R/V      | W="L": Write.          |        |

|        |         | This is the | e MPU interface select    | tion pin.                        |                        |                        |        |

| C86    | I       | C86="H"     | :6800 Series MPU inte     | erface.                          |                        |                        |        |

|        |         | C86="L":    | 8080 Series MPU inte      | erface.                          |                        |                        |        |

|        |         | This pin c  | onfigures the interface   | to be parallel                   | mode or serial mode    | ).                     |        |

|        |         | P/S="H":    | Parallel data input/outp  | put.                             |                        |                        |        |

|        |         | P/S="L":5   | Serial data input.        |                                  |                        |                        |        |

|        |         |             | wing applies depending    |                                  | itus:                  |                        |        |

| P/S    | I       | P/S         | Data/Command              | Data                             | Read/Write             | 4-line SPI Cloc        | :k     |

| 175    | 1       | Н           | A0                        | D0 to D7                         | /RD,/WR                | X                      |        |

|        |         | L           | A0                        | SI (D7)                          | Write only             | SCL (D6)               |        |

|        |         |             | ="L", D0 to D5 must       |                                  |                        |                        |        |

|        |         | ` '         | nd /WR (R/W) are fixe     |                                  |                        |                        |        |

|        |         |             | access mode does NC       |                                  |                        |                        |        |

|        |         |             | pin to enable or disabl   |                                  | lisplay clock oscillat | or circuit.            |        |

| CLS    | I       |             | use internal oscillator:  |                                  |                        |                        |        |

|        |         |             | use external clock inp    | `                                | *                      |                        |        |

|        |         | When CL     | S="L",input the extern    | nal display cloc                 | ek through the CL te   | rminal.                |        |

|        |         |             | e display clock input to  |                                  |                        |                        |        |

|        |         | The follow  | wing is true depending    | on the CLS sta                   |                        |                        | -      |

| CL     | I/O     |             | CLS                       |                                  | CL                     |                        |        |

|        |         |             | "H"                       |                                  | Outp                   | ut                     |        |

|        |         |             | "L"                       |                                  | Inpu                   | t                      |        |

|        |         |             |                           |                                  |                        |                        |        |

Address: Building B4,NO.777,Jianzhu Road,Binhu District,Wuxi City,Jiangsu Province http://www.i-core. cn P.C.: 214072

# Wuxi I-CORE Electronics Co., Ltd. Tab:835-12 rev:B3 Number:AiP31565

Number: AiP31565CR-AX-XS-A040EN

|                 | 1ab:835 | -12 rev:B3                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Number: A1P31565C                                       | K-AA-AS-AU4UEN                                                                                                     |             |  |  |