# NT35532

**Data Sheet**

One-chip RAM-less Driver IC for 16.77M colors Full-HD a-Si GOA TFT LCD with MIPI/SPI/I2C Interface

Version 4.0 2014/07/04

### NT35532

### Index

| Index                                                    | 2   |

|----------------------------------------------------------|-----|

| Reversion History                                        | 5   |

| 1. General Description                                   | 6   |

| 1.1 Purpose of this Document                             | 6   |

| 1.2 General Description                                  | 6   |

| 2. Features                                              | 7   |

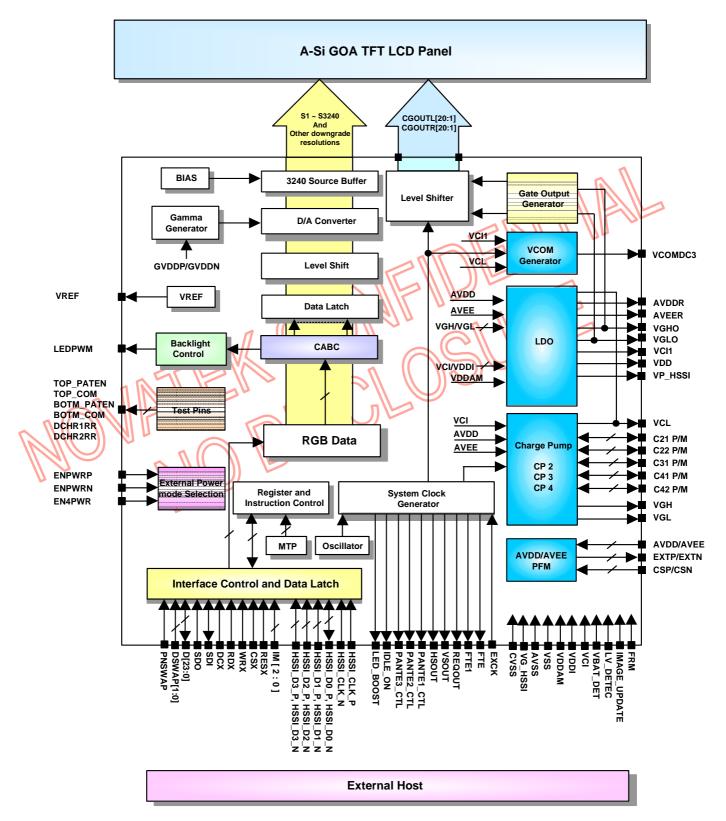

| 3. Block Diagram                                         | 10  |

| 4. Pin Description                                       | 11  |

| 4.1 Pins for Power Input                                 | 11  |

| 4.2 Pins for MIPI Interface                              | 12  |

| 4.3 Pins for SPI / I2C Interface                         | 13  |

| 4.4 Pins for CABC                                        | 13  |

| 4.5 Pins for Interface Control                           | 14  |

| 4.6 Pins for Logic Function Control                      | 15  |

| 4.7 Analog Output for Display Driving                    | 17  |

| 4.8 Panel Control Signals                                | 17  |

| 4.9 Power Supply Pins                                    | 18  |

| 4.10 Test and Dummy Pins                                 | 19  |

| 4.11 Panel Test Pins                                     | 20  |

| 5. Function Descriptions.                                | 21  |

| 5.1 Interfaces (SPI/I2C/MIPI)                            | 21  |

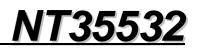

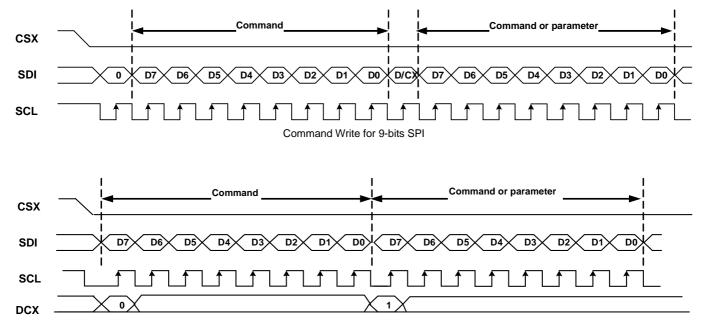

| 5.1.1 SPI Interface                                      | 22  |

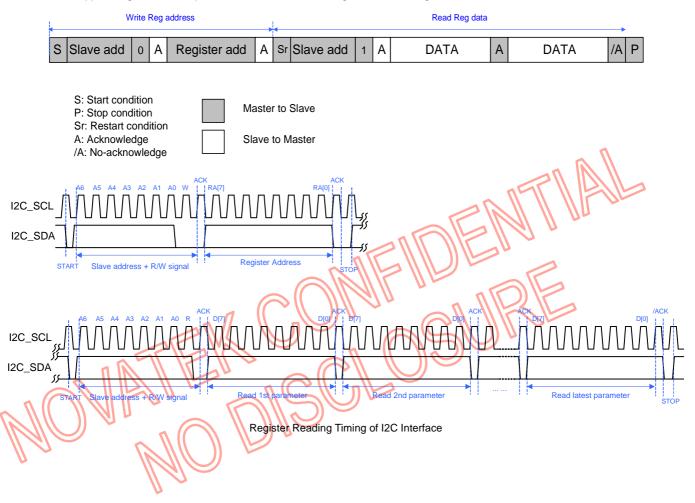

| 5.1.2 I2C Interface                                      | 26  |

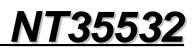

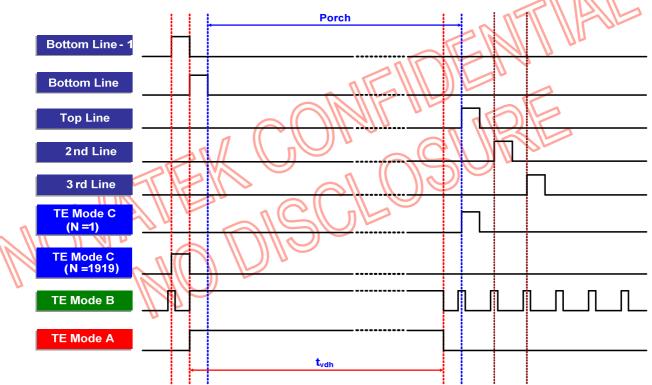

| 5.2 Frame Tearing Effect Interface                       | 29  |

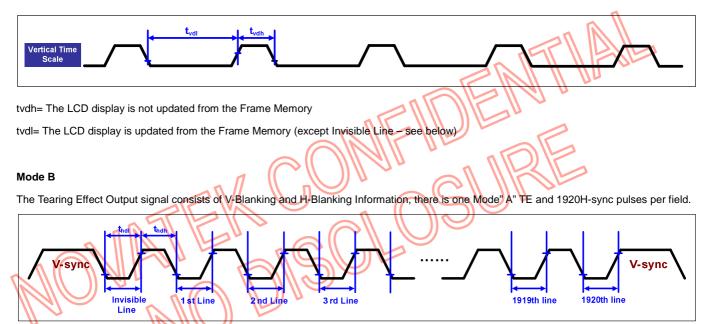

| 5.2.1 Tearing Effect Line Modes                          | 29  |

| 5.2.2 FTE Output Position Setting                        | 31  |

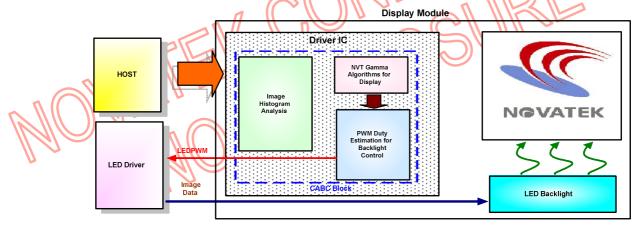

| 5.3 Dynamic Backlight Control Function                   | 32  |

| 5.3.1 Content Adaptive Backlight Control (CABC)          | 33  |

| 5.3.2 Display Backlight Dimming Control                  | 34  |

| 5.3.3 Brightness Control Lines for Backlight             | 35  |

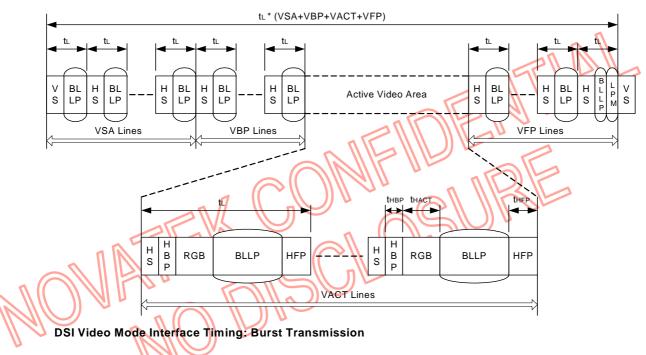

| 5.4 MIPI Interface (Mobile Industry Processor Interface) | 38  |

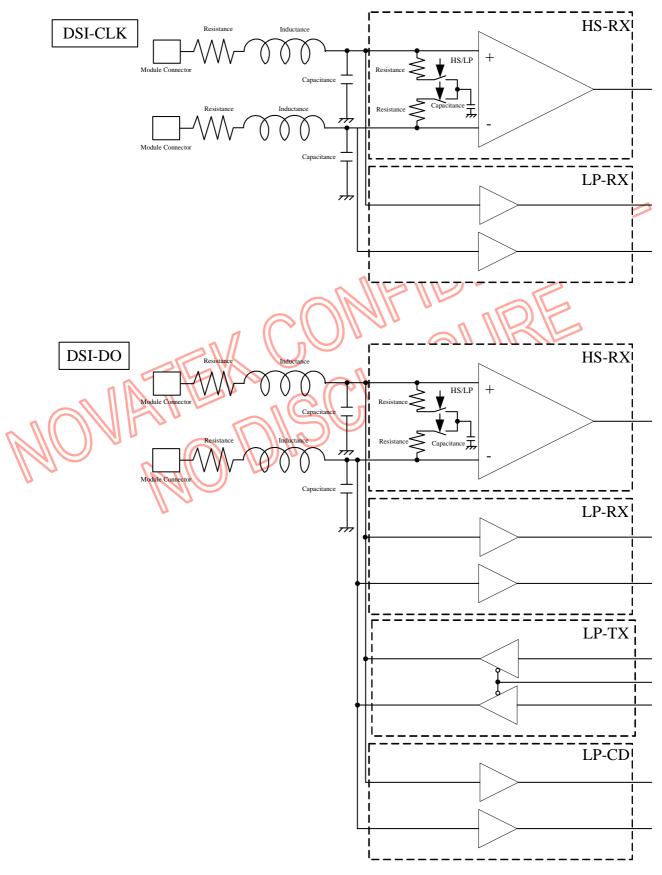

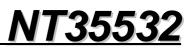

| 5.4.1 Display Module Pin Configuration for DSI           | 39  |

| 5.4.2 Display Serial Interface (DSI)                     | 41  |

| 5.5 Display Reference Clock Function                     | 134 |

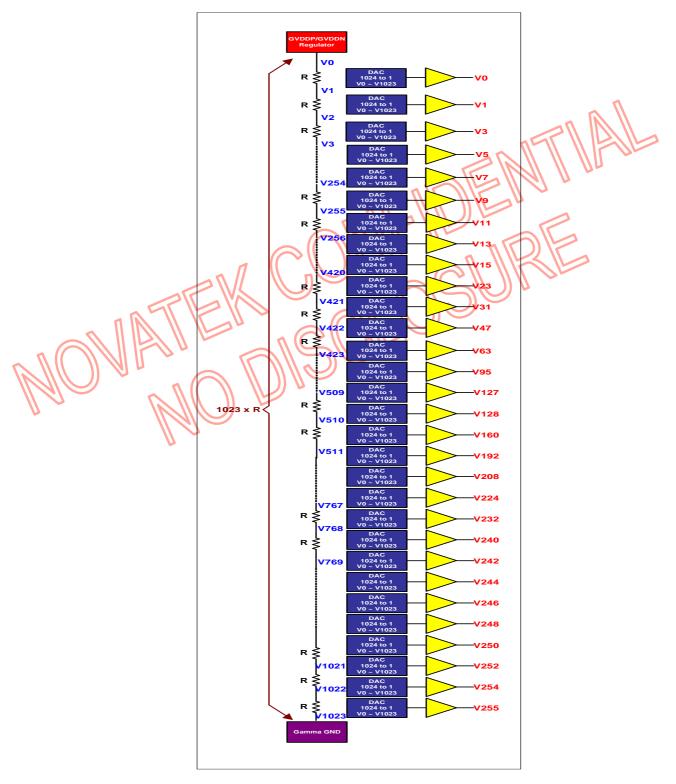

| 5.6 GAMMA Function                                       | 135 |

| 5.7 Reset Function                                       | 136 |

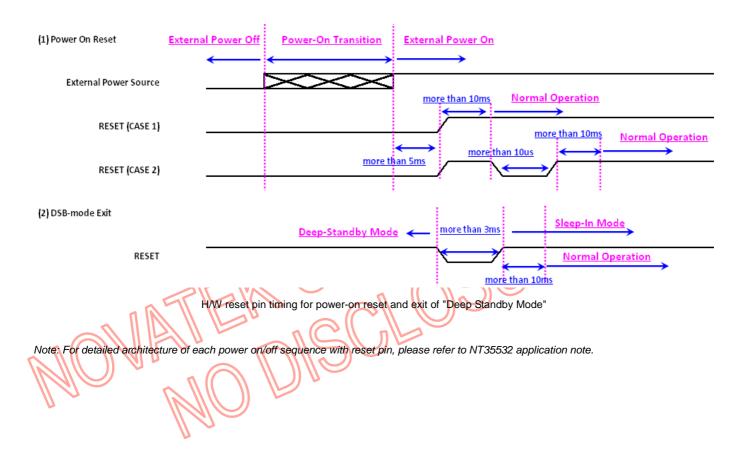

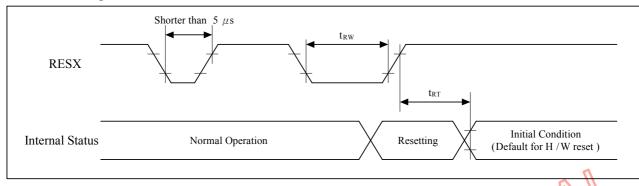

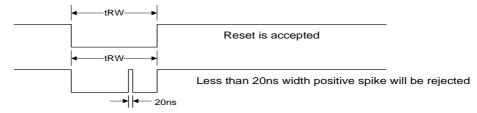

| 5.7.1 Timing of Reset Pin                                | 138 |

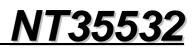

| 5.8 Basic Operation Mode                                 | 139 |

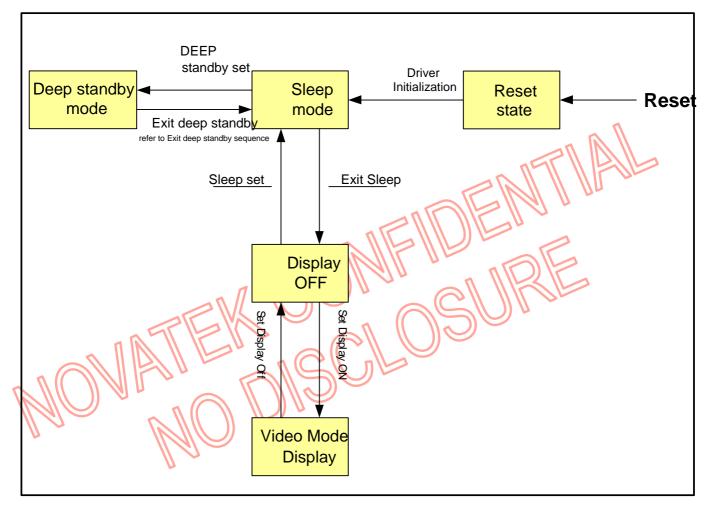

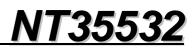

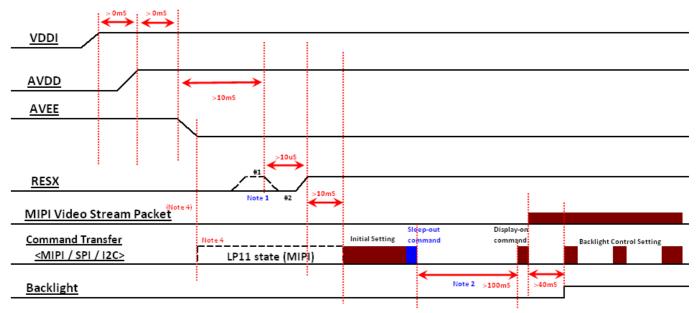

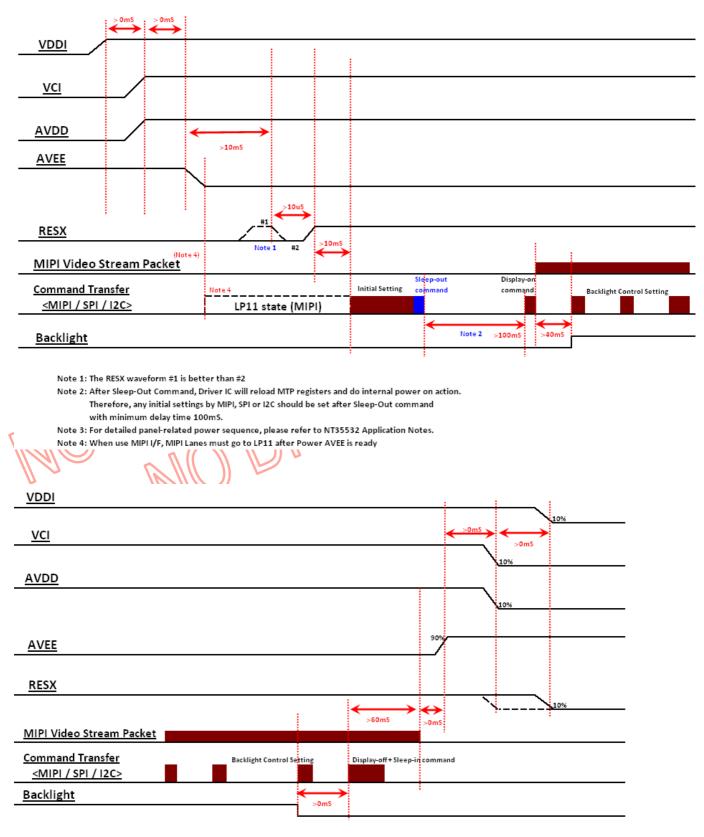

| 5.9 Power On/Off Sequence                                | 140 |

| 5.9.1 Power Supply On/Off setting sequence               | 141 |

|                                                          |     |

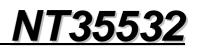

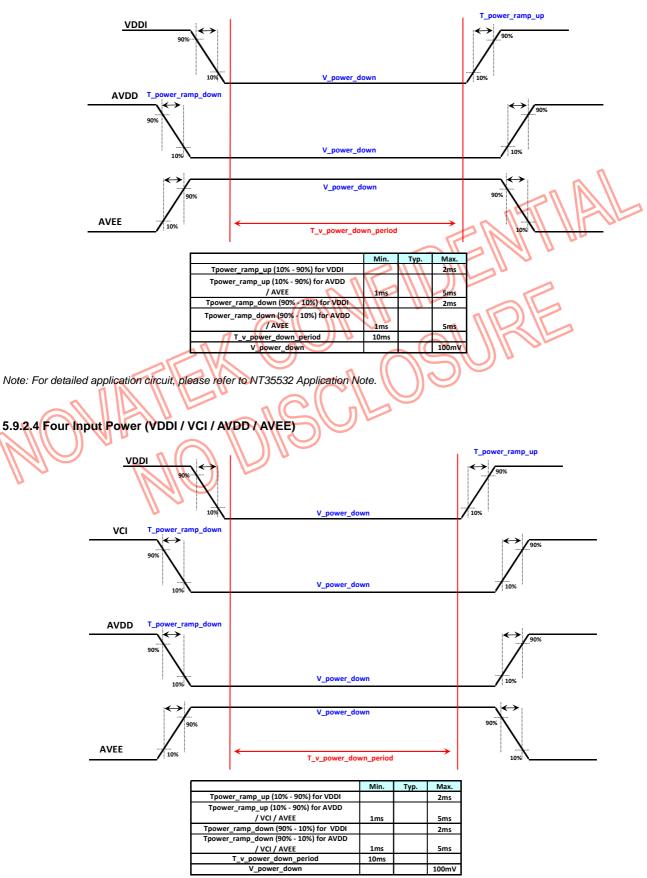

| 5.9.2 Power Ramp-up/down SPEC                                                                 | 144 |

|-----------------------------------------------------------------------------------------------|-----|

| 5.10 Instruction Setting Sequence                                                             | 146 |

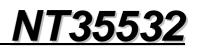

| 5.10.1 Sleep SET/EXIT Sequences                                                               | 146 |

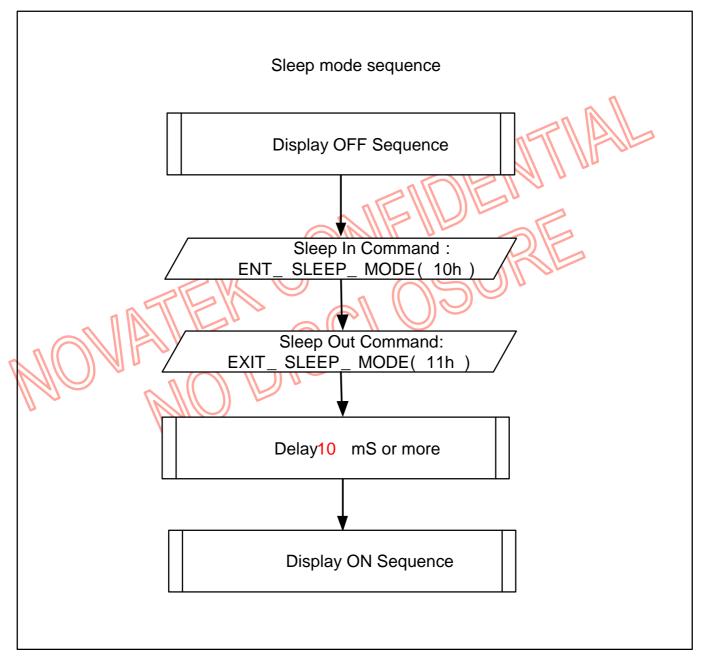

| 5.10.2 Deep Standby Mode ENTER/EXIT Sequences                                                 | 147 |

| 5.11 SLEEP OUT-COMMAND AND SELF-DIAGNOSTIC FUNCTIONS OF THE DISPLAY MODULE                    | 148 |

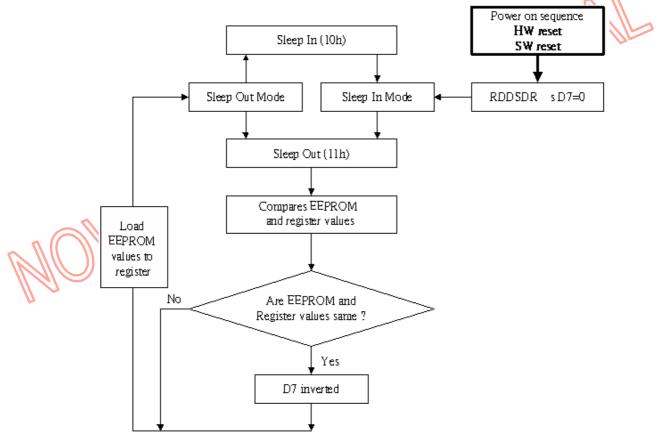

| 5.11.1 Register Loading Detection                                                             | 148 |

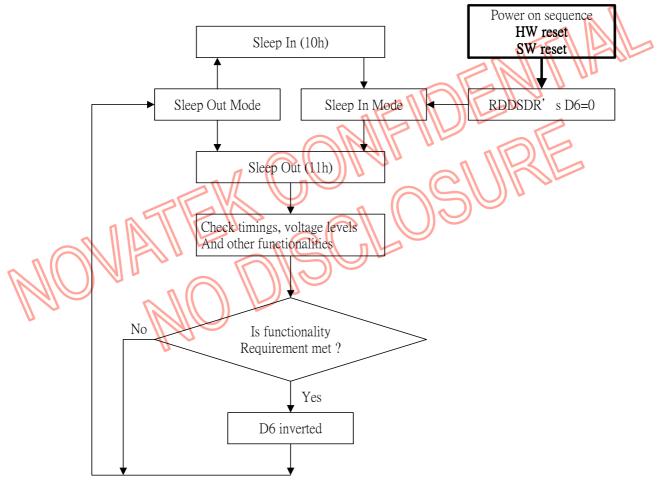

| 5.11.2 Functionality Detection                                                                | 149 |

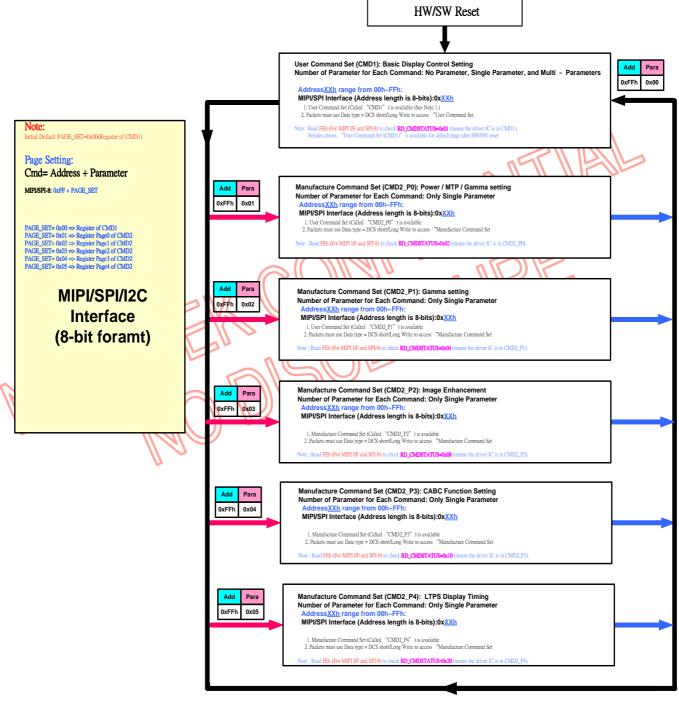

| 6. Command Descriptions                                                                       | 150 |

| Note: At MIPI interface, the page setting command must be sent by single packet transmission, |     |

| or insert 1us delay after page setting command.                                               |     |

| 6.1 User Command Set (Command 1)                                                              |     |

| (00h) NOP: No Operation                                                                       |     |

| (01h) SOFT_RESET: Software Reset                                                              |     |

| (04h) RDID: Read Display ID                                                                   |     |

| (05h) RDNUMED: Read Number of the Error on DSL                                                |     |

| (0Ah) GET_POWER_MODE: Read Display Power Mode                                                 |     |

| (0Bh) GET_ADDRESS_MODE: Get the Display Panel Read Order                                      |     |

| (0Dh) GET_DISPLAY_MODE: Read the Current Display Mode                                         |     |

| (0Eh) GET_SIGNAL_MODE: Get Display Module Signaling Mode                                      |     |

| (0Fh) RDDSDR: Read Display Self-Diagnostic Result                                             | 164 |

| (10h) ENTER_SLEEP_MODE: Enter the Sleep-In Mode                                               |     |

| (11h) EXIT_SLEEP_MODE: Exit the Sleep-In Mode                                                 |     |

| (20h) EXIT_INVERT_MODE: Display Inversion Off                                                 |     |

| (21h) ENTER_INVERT_MODE: Display Inversion On                                                 | 168 |

| (26h) GMASET: Gamma Curves Selection                                                          |     |

| (28h) SET_DISPLAY_OFF: Display Off                                                            | 170 |

| (29h) SET_DISPLAY_ON: Display On                                                              | 171 |

| (34h) SET_TEAR_OFF: Tearing Effect Line OFF                                                   | 172 |

| (35h) SET_TEAR_ON: Tearing Effect Line ON                                                     | 173 |

| (36h) SET_DIRECTION_MODE: Data Direction Access Control                                       | 175 |

| (3Ah) SET_PIXEL_FORMAT: Set the Interface Pixel Format                                        | 177 |

| (44h~45h) SET_TEAR_SCANLINE: Set Tear Line                                                    | 178 |

| (46h) RDSCL : Read Scan Line                                                                  | 180 |

| (4Fh) ENTER_DSTB_MODE: Enter the Deep Standby Mode                                            |     |

| (51h) WRDISBV: Write Display Brightness                                                       |     |

| (52h) RDDISBV: Read Display Brightness                                                        |     |

| (53h) WRCTRLD: Write CTRL Display                                                             |     |

| (54h) RDCTRLD: Read CTRL Display                                                              |     |

| (55h) WRPWRSAVE: Write Power Save                                                             |     |

| (56h) RDPWRSAVE: Read Power Save                                                              |     |

| (5Eh) WRCABCMB: Write CABC Minimum Brightness                                                 |     |

| (5Fh) RDCABCMB: Read CABC Minimum Brightness                                                  | 192 |

|          | (A1h) RDDDBS: Read DDB Start                              | 193 |

|----------|-----------------------------------------------------------|-----|

|          | (A8h) RDDDBC: Read DDB Continue                           | 195 |

|          | (AAh) RDFCS: Read First Checksum                          | 196 |

|          | (ABh) MIPI Error Report                                   | 197 |

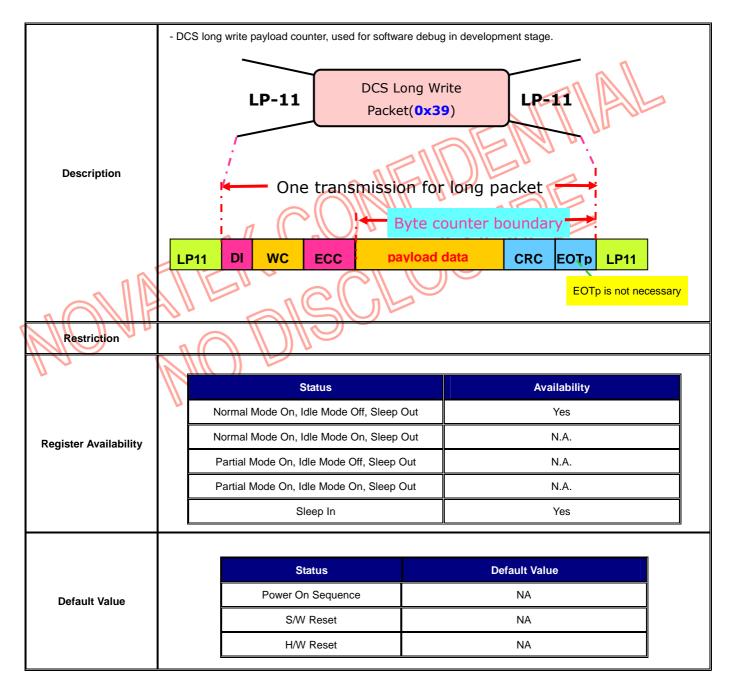

|          | (ACh) DCS long write payload counter                      | 198 |

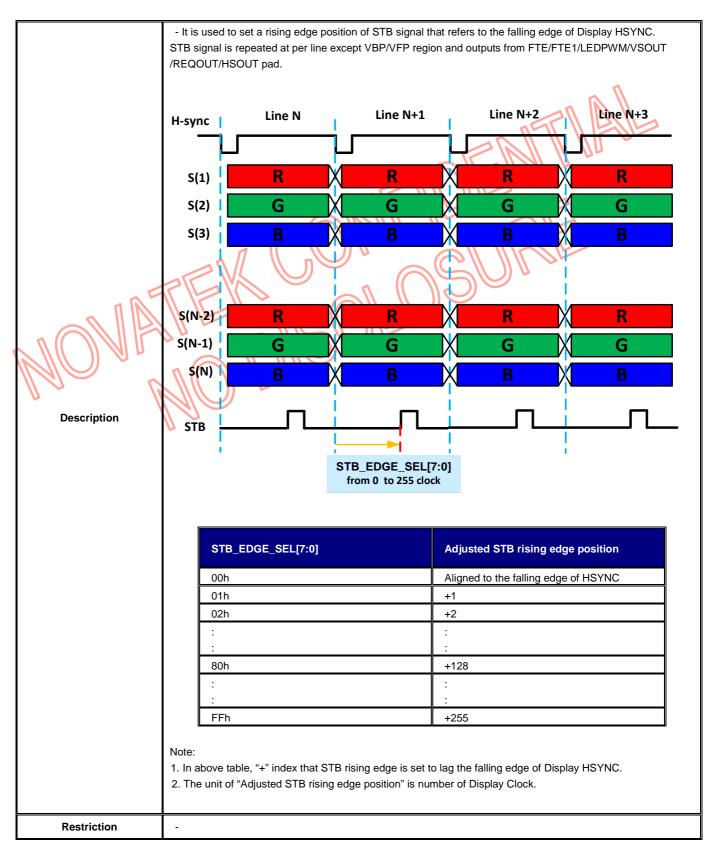

|          | (AEh) STB EDGE POSITION                                   | 199 |

|          | (AFh) RDCCS: Read Continue Checksum                       | 201 |

|          | (BAh) SET_MIPI_LANE and DSI MODE SELECTION                | 202 |

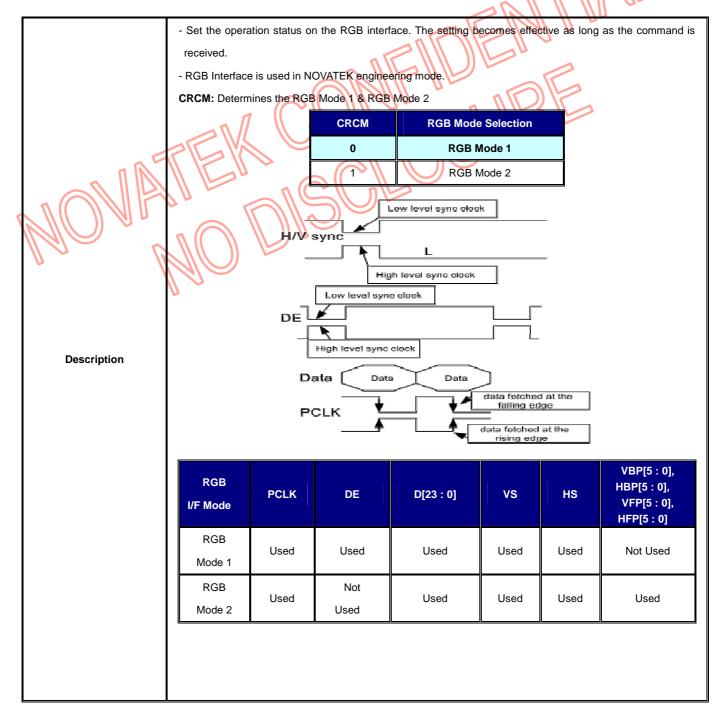

|          | (D2h~D7h) RGBMIPICTRL: RGB-MIPI-Video-Mode Signal Control | 204 |

|          | (D9h) EXCK_CTRL: Display Clock Source Control             | 208 |

|          | (DAh) RDID1: Read ID1                                     | 210 |

|          | (DBh) RDID2: Read ID2                                     | 211 |

|          | (DCh) RDID3: Read ID3                                     | 212 |

|          | (E1h) IDLEMODE_BL_Control: Write IDLEMODE_BL_Control      | 213 |

|          | (E2h) IDLEMODE_BL_Control: Read IDLEMODE_BL_Control       | 215 |

|          | (F3h) MULTIIF: Multi-Interface Function                   | 217 |

|          | (F4h) Novatek ID: Read Novatek ID                         | 219 |

|          | (F5h) IF_TEST: INTERFACE TEST                             | 220 |

|          | (F6h~F7h) EXCK_CTRL: Display Clock Source Control         | 221 |

| 10       | (F8h) I2C_SLAVE_ADDR: I2C Slave Address                   | 222 |

| ILAI     | (F9h) PIXEL_EXTEN: PIXEL EXTENSION FORMAT                 | 223 |

|          | (FBh) RELOAD CMDI                                         | 224 |

|          | (FEh) RD_CMDSTATUS: Read the Current Register Set         | 225 |

|          | (FFh) CMD Page Select.                                    | 227 |

| 7. Elect | rical Characteristics                                     | 228 |

| 7.1      | ABSOLUTE MAXIMUM RATINGS                                  | 228 |

| 7.2      | DC CHARACTERISTICS                                        | 229 |

|          | 7.2.1 Basic Characteristics                               | 229 |

|          | 7.2.2 Current Consumption                                 | 230 |

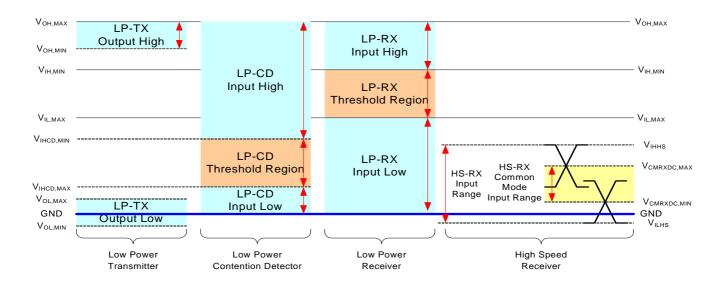

|          | 7.2.3 MIPI DC Characteristics                             | 231 |

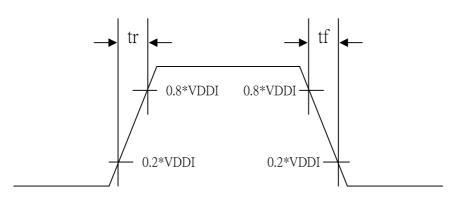

| 7.3      | AC CHARACTERISTICS                                        | 232 |

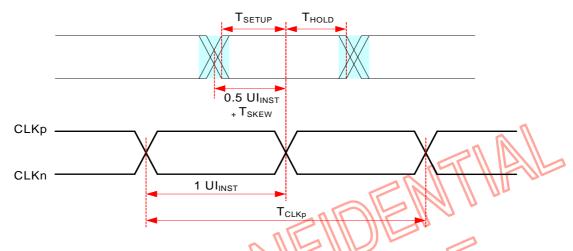

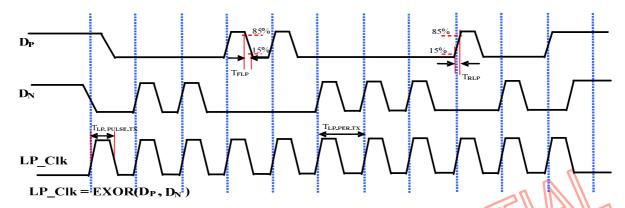

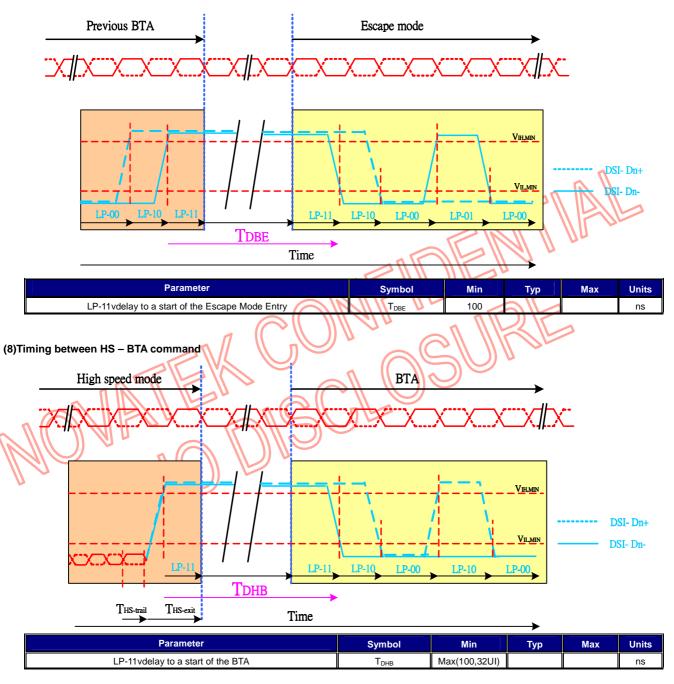

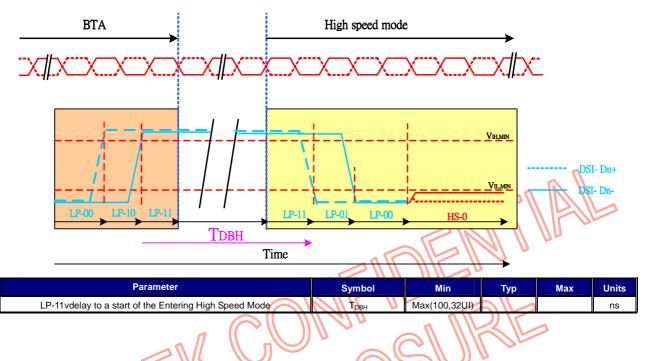

|          | 7.3.1 MIPI Interface Characteristics                      | 232 |

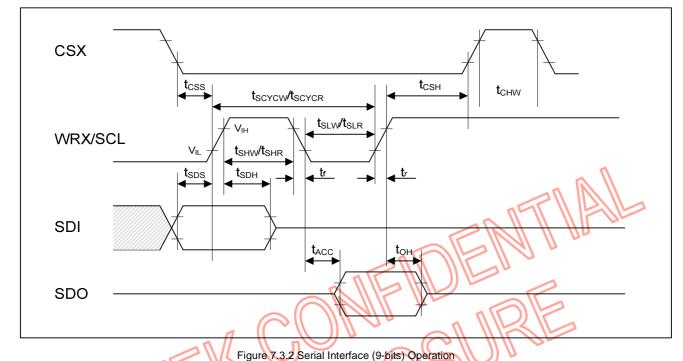

|          | 7.3.2 Serial Interface Timing Characteristics             | 241 |

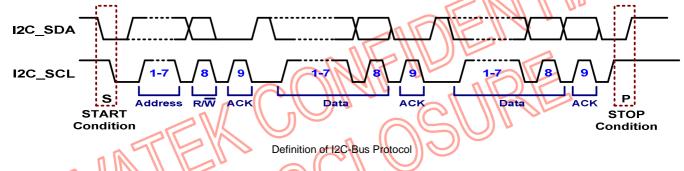

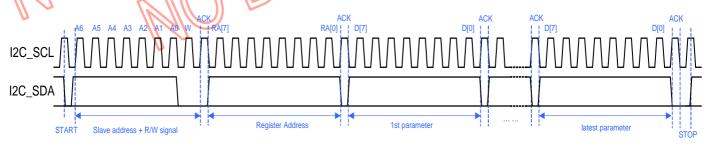

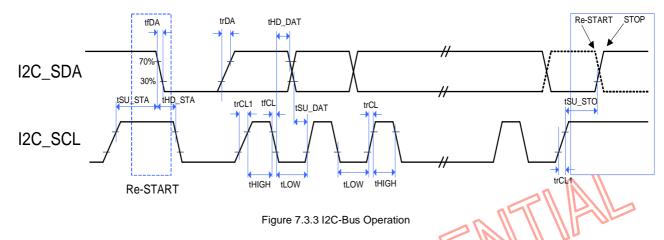

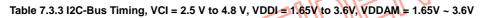

|          | 7.3.3 I2C Bus Characteristics                             | 242 |

|          | 7.3.4 Reset Timing Characteristics                        | 244 |

#### **Reversion History**

| Version | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Prepared<br>by            | Checked<br>by | Approved<br>by  | Date       |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------|-----------------|------------|

| 0.00    | Preliminary Version                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Steve Chiang              | Charley Chou  |                 | 2013/04/12 |

| 0.01    | <ol> <li>Modify Source driver output (page 7.)</li> <li>Modify ENPWRP/ENPWRN to digital output (page 16.)</li> <li>Modify CGOUTL[18:1] and CGOUTR[18:1] to CGOUTL[20:1] and<br/>CGOUTR[20:1] (page 17.)</li> <li>Add Block diagram (page 10.)</li> <li>Add HBM mode in 0x5300 (page 184.)</li> <li>Add 0xE1h IDLE MODE BL Control (page 214.)</li> <li>Add 0xBAh DSI mode selection(page.202.)</li> <li>Add Output Voltage Level(page.9)</li> </ol>                                                                                                                                 | Aaron Tan                 | Charley Chou  |                 | 2012/09/17 |

| 0.02    | <ol> <li>Add CGTEST3, CGTEST4 (page. 19)</li> <li>Add HBP and HFP application restriction (page. 207)</li> <li>Modify VP_HSSI, VDD typical voltage level (page.231, 233)</li> <li>Modify parameters of table "Required Peripheral Timing" (P.133)</li> </ol>                                                                                                                                                                                                                                                                                                                        | Aaron Tan<br>Steve Chiang | Charley Chou  | 2               | 2013/03/28 |

| 0.03    | <ol> <li>Modify "Block Diagram" (page.10)</li> <li>"TOP_PATEN", "TOP_COM", "BOTM_PATEN", "BOTM_COM" pin<br/>description move to "Panel Test Pins" block. (page.20)</li> <li>Modify "Required Peripheral Timing" Table. (page.133)</li> <li>Modify OSC spec: 14MHz -&gt; 14.66MHz (page.134)</li> <li>Modify VDDAM range : 1.65 ~ 3.6V (page.8,11,229,231,241-244)</li> <li>Remove 3D function (include BCh command) description.<br/>(page.8,9,67,154,188,204)</li> <li>Modify VBP/VFP/HBP/HFP constraints. (page.206)</li> <li>Add current consumption data. (page.230)</li> </ol> | Steve Chiang              | Chris Chen    | Charley<br>Chou | 2013/06/07 |

| 1.0     | 1.Modify Block diagram. (page.10)<br>2.Modify Display Module Pin Configuration for DSI.(page.39,40)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Steve Chiang              | Chris Chen    | Charley<br>Chou | 2013/07/19 |

| 1.1     | 1.Modify LEDPWM frequency. (page.36)<br>2.Modify MIPI DSI mode selection.(page.202)<br>3.Modify HBP unit. (page.206)                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Steve Chiang              | Chris Chen    | Charley<br>Chou | 2013/08/16 |

| 1.2     | 1.Modify the formula of LEDPWM frequency. (page.36)<br>2.Modify power ramp up spec. (page.144, 145)<br>3.Add the constraint of "page setting command" at MIPI I/F. (page.150)<br>4.Modify the typo: $80MHz \rightarrow 80Mbps.(page.232)$                                                                                                                                                                                                                                                                                                                                           | Steve Chiang              | Chris Chen    | Charley<br>Chou | 2013/11/21 |

| 2.0     | 1.Modify Power Supply On/Off setting sequence. (page.141-143)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Steve Chiang              | Chris Chen    | Charley<br>Chou | 2014/01/06 |

| 3.0     | 1.Modify the pin description of VCI pad (When 2-2 & 3-PWR mode, do not<br>need VCI stabilize cap). (page.11)<br>2.Modify the pin description of IDLE_ON, LED_BOOST pad. (page.19)                                                                                                                                                                                                                                                                                                                                                                                                   | Steve Chiang              | Chris Chen    | Charley<br>Chou | 2014/02/10 |

| 4.0     | 1.Modify the pin description of VSOUT,HSOUT pad. (page.19)<br>2.Remove Section5.2 "Display Data PATH".<br>3.Modify the typo of 0xD9h EXCK_CTRL register. (page.208)<br>4.Modify the typo of Gamma reference voltage spec. (page.229)                                                                                                                                                                                                                                                                                                                                                | Steve Chiang              | Chris Chen    | Max Tang        | 2014/07/04 |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                           |               |                 |            |

#### 1. General Description

#### 1.1 Purpose of this Document

This document has been created to provide complete reference specifications for the NT35532. IC designers, testing engineers and application engineers should refer to these specifications for circuits design, quality/performance control, and IC applications for customer.

#### **1.2 General Description**

The NT35532 device is a single-chip RAM-less solution for a-Si GOA TFT LCD that incorporates gate drivers, a timing controller with glass interface level-shifters, a VCOM driver and a glass power supply circuit.

The NT35532 can support MIPI, SPI and I2C interface. The source resolution can be adjusted from 720RGB to 1080RGB and the gate resolution also can be set from 1024 lines to 1920 lines. Regarding the detailed resolution setting, please refer to NT35532 Application Note.

The NT35532 is also able to make gamma correction settings separately for RGB dots to allow benign adjustments to panel characteristics, resulting in higher display qualities. The IC includes internal boosters that generate the LCD driving voltage, breeder resistance and voltage follower circuit for the LCD driver. A deep standby mode is also supported for lower power consumption.

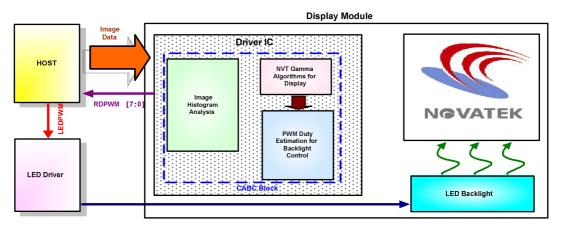

The NT35532 also supports CABC function for the backlight control. It's able to reduce the total power consumption of display module

significantly.

This LSI is suitable for small or medium-sized portable mobile solutions requiring long-term driving capabilities, including bi-directional pagers, digital audio players, cellular phones and handheld PDA.

#### 2. Features

- Single-chip Full-HD a-Si GOA Controller / Driver.

- Principal Display Resolution

- 1080RGB x 1920 (1:1 Multiplexer for source driver, Source output from S1 to S1620, and S1621 to S3240)

- 1050RGB x 1680 (1:1 Multiplexer for source driver, Source output from S1 to S1575, and S1666 to S3240)

- 1050RGB x 1400 (1:1 Multiplexer for source driver, Source output from S1 to S1575, and S1666 to S3240)

- 1024RGB x 1280 (1:1 Multiplexer for source driver, Source output from S1 to S1536, and S1705 to S3240)

- 1000RGB x 1600 (1:1 Multiplexer for source driver, Source output from S1 to S1500 and S1741 to S3240)

- 960RGB x 1440 (1:1 Multiplexer for source driver, Source output from S1 to S1440, and S1801 to S3240)

- 960RGB x 1280 (1:1 Multiplexer for source driver, Source output from S1 to S1440, and S1801 to S3240)

- 900RGB x 1600 (1:1 Multiplexer for source driver, Source output from S1 to S1350, and S1891 to S3240)

- 900RGB x 1440 (1:1 Multiplexer for source driver, Source output from S1 to S1350, and S1891 to S3240)

- 850RGB x 1360 (1:1 Multiplexer for source driver, Source output from \$1 to \$1275, and \$1966 to \$3240)

- 810RGB x 1440 (1:1 Multiplexer for source driver, Source output from S1 to S1215, and S2026 to S3240)

- 800RGB x 1280 (1:1 Multiplexer for source driver, Source output from S1 to S1200, and S2041 to S3240).

- 768RGB x 1366 (1:1 Multiplexer for source driver, Source output from S1 to S1152, and S2089 to S3240)

- 720RGB x 1280 (1:1 Multiplexer for source driver, Source output from S1 to S1080, and S2161 to S3240)

#### Display Modes

- Full Color Mode: 16.77M-colors

- Reduced Color Mode: 262K-colors

- Reduced Color Mode: 65K-colors

- Only supported Normal Display Mode

- Interface

- MIPI DSI Interface (D-PHY: V1.1 , DSI:1.01.00, DCS:1.01.00)

MIPI I/F Supported 2, 3 or 4 data lanes (Lane number is selected by register Bah of CMD1 in MIPI LP mode, and this register can be programmed by MTP)

- I2C Interface

- SPI Interface

- Multi-interface (MIPI + SPI (8/9-bits) or MIPI + I2C by HW pin or register setting)

#### Display Features

- Individual gamma correction setting for RGB dots

- Deep standby function

RE

#### On Chip Function

DC/DC converter

**JOVATEK**

- VCOM voltage generator

- Supports control signals (CGOUTR1~R20, CGOUTL1~L20) to gate driver in the LCD panel

- Provide OTP (1 time) to store related Power, a-Si setting, and gamma setting

- Provide MTP (3 times) to store VCOM, ID1, ID2, ID3 and DDB calibration

- Oscillator for display clock generation

- On module checksum checking

- Image enhancement technology

#### • Content Adaptive Backlight Control (CABC) Function

- Histogram analysis & data process

- Dimming control

- Only supported in full display mode

- Supply Voltage Range

- Analog supply voltage range VCI to AVSS: 2.5V to 4.8V

- I/O supply voltage range for VDDI to VSS: 1.65V to 3.6V

- MIPI DSI supply voltage range for VDDAM to VSS: 1.65V to 3.6V

- (VDDAM can connect to VDDI or VCI if its operation voltage is available)

- Analog supply voltage range for AVDD to AVSS: 4.5V to 6V

- Analog supply voltage range for AVEE to AVSS: -4.5V to -6V

Output Voltage Level

- Source output voltage level: ( GVDDP ~ +0.2V ) and ( -0.2V ~ GVDDN )

- Gamma voltage range: GVDDP = 3.5V ~ 5.5V (10mV/step)

GVDDN = -3.5V ~ -5.5V (10mV/step)

■ Positive gate driver output voltage level: VGH to AVSS = 2 x AVDD, 2 x AVDD – VCL, 2 x AVDD – AVEE, 3 x AVDD – VCL,

3 x AVDD - AVEE

■ Negative gate driver output voltage level: VGL to AVSS = AVEE – VCI1, 2 x AVEE, 2 x AVEE – VCI1, 2 x AVEE - AVDD

#### VGLO= -4V ~ -18V (100mV/step)

Common electrode output voltage level: VCOMDC3 = -4V to +1V (10mV/step)

2014/07/04

#### 3. Block Diagram

#### 4. Pin Description

#### 4.1 Pins for Power Input

| Symbol          | Pad Type                 | Description                                                                                                                                                                                                                                 |  |  |  |  |  |

|-----------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| VCI             | Power Supply             | <ul> <li>Power supply to the liquid crystal power supply analog circuit. Connect VCI to an external power supply with 2-1PWR and 4 PWR modes (VCI = 2.5V to 4.8V).</li> <li>In 2-2PWR and 3 PWR modes, VCI will be a LDO output.</li> </ul> |  |  |  |  |  |

| VDDI            | Power Supply             | - Power supply to the I/O.<br>- VDDI = 1.65V to 3.6V                                                                                                                                                                                        |  |  |  |  |  |

| VDDI_DC         | Power Supply             | - Connect to VDDI for preventing noise.                                                                                                                                                                                                     |  |  |  |  |  |

| VDDAM           | Power Supply             | - Power supply for MIPI interface.<br>- VDDAM = 1.65V ~ 3.6V                                                                                                                                                                                |  |  |  |  |  |

| VSS             | Power Ground             | - Ground for digital logic. VSS = 0V                                                                                                                                                                                                        |  |  |  |  |  |

| AVSS<br>AVSS_DC | Power Ground             | <ul> <li>Ground for the analog unit (regulator, liquid crystal power supply circuit). AVSS = 0V.</li> <li>In case of COG, connect AVSS to VSS on the FPC to prevent noise.</li> </ul>                                                       |  |  |  |  |  |

| CVSS            | Power Ground             | <ul> <li>Ground for the charge pump. CVSS = 0V.</li> <li>In case of COG, connect CVSS to VSS on the FPC to prevent noise.</li> </ul>                                                                                                        |  |  |  |  |  |

| VG_HSSI         | Power Ground             | <ul> <li>Ground for the High Speed Interface regulator. VG_HSSI= 0V.</li> <li>In case of COG, connect VG_HSSI to VSS on the FPC to prevent noise.</li> </ul>                                                                                |  |  |  |  |  |

| AVDD            | Power Input              | <ul> <li>Positive input analog power for driver IC use.</li> <li>It can be generated by "Internal PFM" or supported by "external PMIC".</li> </ul>                                                                                          |  |  |  |  |  |

| AVEE            | Power Input              | <ul> <li>Negative input analog power for driver IC use.</li> <li>It can be generated by "Internal PFM" or supported by "external PMIC".</li> </ul>                                                                                          |  |  |  |  |  |

| VBAT            | Powe input<br>(AVDD-VSS) | - Battery voltage detection input signal.<br>- If not used, please tie it to VSS.                                                                                                                                                           |  |  |  |  |  |

| VCI_DET         | Powe input<br>(VCI-VSS)  | <ul> <li>Battery voltage detection input signal.</li> <li>It is used to connect to VCI.</li> </ul>                                                                                                                                          |  |  |  |  |  |

| EXTP            | Output                   | <ul> <li>Control output for gate of NMOS in positive internal PFM converter when ENPWRP = AVSS.</li> <li>If not used, please let this pin open.</li> </ul>                                                                                  |  |  |  |  |  |

| EXTN            | Output                   | <ul> <li>Control output for gate of PMOS in negative internal PFM converter when ENPWRN = AVSS.</li> <li>If not used, please let this pin open.</li> </ul>                                                                                  |  |  |  |  |  |

| CSP             | Analog Input             | <ul> <li>Voltage signal for sensing external inductor current in positive Internal PFM converter when ENPWRP = AVSS.</li> <li>If not used, please let this pin open.</li> </ul>                                                             |  |  |  |  |  |

| CSN             | Analog Input             | <ul> <li>Voltage signal for sensing external inductor current in negative Internal PFM converter where ENPWRN = AVSS.</li> <li>If not used, please let this pin open.</li> </ul>                                                            |  |  |  |  |  |

2014/07/04

#### 4.2 Pins for MIPI Interface

| Symbol        | Pad Type   | Description                                                                                     |

|---------------|------------|-------------------------------------------------------------------------------------------------|

|               |            | - DSI_CLK positive/ negative in MIPI interface.                                                 |

|               |            | - HSSI_CLK_P/N are differential small amplitude signals. Ensure the trace length is shortest so |

|               | MIDI Input | that the – COG resistance is less than 10 ohm.                                                  |

| HSSI_CLK_P/N  | MIPI Input | - For MIPI I/F, if deep standby mode is used, please pull HSSI_CLK_P/N to VSS after issuing     |

|               |            | deep standby command                                                                            |

|               |            | - If not used, please tie to VSS.                                                               |

|               |            | - MIPI positive/negative data signal line.                                                      |

|               |            | - HSSI_D0_P/N are differential small amplitude signals. Ensure the trace length is shortest so  |

| HSSI_D0_P/N   | MIPI I/O   | that the COG resistance is less than 10 ohm.                                                    |

| H33I_D0_F/N   | WIFT VO    | - For MIPI I/F, if deep standby mode is used, please pull HSSI_D0_P/N to VSS after issuing      |

|               |            | deep standby command                                                                            |

|               |            | - If not used, please tie to VSS.                                                               |

|               |            | - MIPI positive/ negative data signal line.                                                     |

|               |            | - HSSI_D1_P/N are differential small amplitude signals. Ensure the trace length is shortest so  |

| HSSI_D1_P/N   | MIPHnput   | that the COG resistance is less than 10 ohm.                                                    |

| H33I_D1_F/N   |            | - For MIPI I/F, if deep standby mode is used, please pull HSSI_D1_P/N to VSS after issuing      |

|               |            | deep standby command                                                                            |

|               |            | - If not used, please tie to VSS.                                                               |

|               |            | - MIP( positive/ negative data signal line.                                                     |

| N ~           |            | HSSI_D2_P/N are differential small amplitude signals. Ensure the trace length is shortest so    |

| HSSI_D2_P/N   | MIPI Input | that the COG resistance is less than 10 ohm.                                                    |

| H33I_D2_F/N   | Mirinput   | - For MIPI I/F, if deep standby mode is used, please pull HSSI_D2_P/N to VSS after issuing      |

|               |            | deep standby command                                                                            |

|               |            | - If not used, please tie to VSS.                                                               |

|               |            | - MIPI positive/ negative data signal line.                                                     |

|               |            | - HSSI_D3_P/N are differential small amplitude signals. Ensure the trace length is shortest so  |

| HSSI_D3_P/N   | MIPI Input | that the COG resistance is less than 10 ohm.                                                    |

| 1001_00_17/14 |            | - For MIPI I/F, if deep standby mode is used, please pull HSSI_D3_P/N to VSS after issuing      |

|               |            | deep standby command.                                                                           |

|               |            | - If not used, please tie to VSS.                                                               |

## NT35532

#### 4.3 Pins for SPI / I2C Interface

| Symbol           | Pad Type                       | Description                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                                | - Chip select input pin of NT35532.                                                                                                                                                                                                                                                                                                                                                                          |

| CSX              | Digital Input                  | CSX = "0" (VSS): Selected (accessible)                                                                                                                                                                                                                                                                                                                                                                       |

| CSX              | (VDDI – VSS)                   | CSX = "1" (VDDI): Unselected (not accessible)                                                                                                                                                                                                                                                                                                                                                                |

|                  |                                | - If not used, please pull it to VDDI.                                                                                                                                                                                                                                                                                                                                                                       |

| DCX              | Input                          | - This pin is used for SPI 8-bits I/F.<br>- If not used, please tie this pin to VDDI.                                                                                                                                                                                                                                                                                                                        |

|                  |                                | - WRX: Novatek engineering mode.                                                                                                                                                                                                                                                                                                                                                                             |

| WRX              | Digital Input                  | - SCL: A synchronous clock signal in serial interface (SPI) operation                                                                                                                                                                                                                                                                                                                                        |

| (SCL/ I2C_SCL)   | (VDDI – VSS)                   | - I2C_SCL: Serial input / output clock in I2C interface operation.                                                                                                                                                                                                                                                                                                                                           |

|                  |                                | - If not used, please pull it to VDDI.                                                                                                                                                                                                                                                                                                                                                                       |

| SDI<br>(I2C_SDA) | Digital I/O<br>(VDDI – VSS)    | <ul> <li>SDI: Serial data input pin (SDI) in serial interface (SPI) operation.</li> <li>I2C_SDA: Serial input/output data in I2C-Bus interface operation.</li> <li>If not used, please pull it to VSS.</li> </ul>                                                                                                                                                                                            |

| SDO              | Digital Output<br>(VDDI – VSS) | <ul> <li>Serial data output pin (SDO) in serial interface operation. If the host places the SDI line into high-impedance state during the read intervals, then the SDI and SDO can be tied together.</li> <li>If not used, please let it floating.</li> <li>If user wants to save one trace of glass and system can support SDI/SDO share one wire, you can let SDO tie to SDI together on glass.</li> </ul> |

| 4.4 Pins for     |                                |                                                                                                                                                                                                                                                                                                                                                                                                              |

### 4.4 Pins for CABC

| Symbol | Pad Type                       | Description                                                                                                                                                                                        |

|--------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

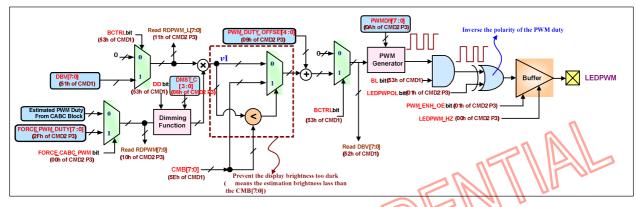

|        | Digital Output<br>(VDDI – VSS) | - This pin is used to connect to the external LED driver of panel backlight control.                                                                                                               |

| LEDPWM |                                | <ul> <li>PWM type control signal for determining brightness of the LED backlight.</li> <li>The duty width of this LEDPWM signal is set by an 8-bits value to determine the duty from 0%</li> </ul> |

|        |                                | (Low) and 100% (High).<br>- If not used, please open this pin.                                                                                                                                     |

|        |                                |                                                                                                                                                                                                    |

#### 4.5 Pins for Interface Control

| Symbol  | Pad Type                      |      | Description |       |        |                                                  |                                                                                 |                      |  |  |

|---------|-------------------------------|------|-------------|-------|--------|--------------------------------------------------|---------------------------------------------------------------------------------|----------------------|--|--|

|         |                               | Sele | ects        | s the | interf | ace to MPU (VDDI –VSS am                         | plitude signal).                                                                |                      |  |  |

|         |                               | I    | M2          | IM1   | IMO    | Interface Selection                              | Data Pins                                                                       | Available<br>Colors  |  |  |

|         |                               |      | 0           | 0     | 0      | MIPI + I2C                                       | MIPI : HSSI_D0_P/N ~<br>HSSI_D3_P/N<br>I2C : I2C_SDA                            | 65k, 262k,<br>16.77M |  |  |

|         |                               |      | 0           | 0     | 1      | Reserved                                         | Reserved                                                                        | Reserved             |  |  |

|         |                               |      | 0           | 1     | 0      | MIPI + SPI (9-bits)<br>(SCL rising edge trigger) | MIPI : HSSI_D0_P/N ~<br>HSSI_D3_P/N<br>SPI : SDI, SDO                           | 65k, 262k,<br>16.77M |  |  |

| IM2 – 0 | Digital Input<br>(VDDI – VSS) |      | 0           | 1     | 1      | MIPI + SPI (8-bits)<br>(SCL rising edge trigger) | MIPI :HSSI_D0_P/N ~<br>HSSI_D3_P/N<br>SPI : SDI, SDO                            | 65k, 262k,<br>16.77M |  |  |

|         |                               |      | 1           | 0     | 0      | Reserved                                         | Reserved                                                                        | Reserved             |  |  |

|         |                               |      | 1           | 0     | 1      | Reserved                                         | Reserved                                                                        | Reserved             |  |  |

|         |                               |      | 1           | 1     | 0      | MIPI Interface                                   | HSSI_D0_P/N, HSSI_D1_P/N<br>HSSI_D2_P/N, HSSI_D3_P/N                            | 65k, 262k,<br>16.7M  |  |  |

| ~       |                               |      | 1           | 1     | 1      | Reserved                                         | Reserved                                                                        | Reserved             |  |  |

| NO      | NFN<br>AV                     | No   |             | a     | nd Da  | ata Lane to VP_HSSI.                             | ′011b and do not use MIPI I/F, please<br>nterface function also can be set by C |                      |  |  |

#### 4.6 Pins for Logic Function Control

| Symbol     | Pad Type                       |                                                                                                                                                                                                  |                                                                                                                                                                                                                                                  |                                          |           |          | I        | Descrip | tion |         |          |           |          |     |

|------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------|----------|----------|---------|------|---------|----------|-----------|----------|-----|

| RESX       | Digital Input<br>(VDDI – VSS)  | Lo                                                                                                                                                                                               | <ul> <li>This signal will reset the device and must be applied to properly initialize the chip. Signal is active Low.</li> <li>There is no internal pull high resistor for this pin.</li> </ul>                                                  |                                          |           |          |          |         |      |         |          |           |          |     |

| ЕХСК       | Digital Input<br>(VDDI – VSS)  | - Th                                                                                                                                                                                             | <ul> <li>External Clock Source to Driver IC.</li> <li>This external clock frequency range is 9MHz to 40MHz.</li> <li>If not used, please tie it to VSS.</li> </ul>                                                                               |                                          |           |          |          |         |      |         |          |           |          |     |

| FTE        | Digital Output<br>(VDDI – VSS) | - Th                                                                                                                                                                                             | ne output                                                                                                                                                                                                                                        | id pulse si<br>voltage le<br>, please le | evel of F | TE pin i | s deterr |         |      | zing RA | M data v | write ope | erations |     |

| FTE1       | Digital Output<br>(VDDI – VSS) | - Th                                                                                                                                                                                             | <ul> <li>This signal is used for noise sensing of TP (Generating a pulse output per scan line from NT35532).</li> <li>The output voltage level of FTE1 pin is determined by VDDI.</li> <li>If not used, please let this pin floating.</li> </ul> |                                          |           |          |          |         |      |         |          |           |          |     |

| REQOUT     | Digital Output<br>(VDDI – VSS) | - Th                                                                                                                                                                                             | <ul> <li>This signal is used to notice Host to input frame data in interval driving mode.</li> <li>The output voltage level of REQOUT pin is determined by VDDI.</li> <li>If not used, please let this pin floating.</li> </ul>                  |                                          |           |          |          |         |      |         |          |           |          |     |

|            |                                | <ul> <li>PNSWAP and DSWAP are used for the combination of polarity swap and data lane swap of MIPI.</li> <li>If not used, please assigned default state as PNSWAP=1b, DSWAP[1:0]=11b.</li> </ul> |                                                                                                                                                                                                                                                  |                                          |           |          |          |         |      |         |          |           |          |     |

| Male       | la I                           | PN                                                                                                                                                                                               | NSWAP                                                                                                                                                                                                                                            | DSWAP<br>[1:0]                           | D2+       | D2-      | D1+      | D1-     | CLK+ | CLK-    | D0+      | D0-       | D3+      | D3- |

|            |                                |                                                                                                                                                                                                  |                                                                                                                                                                                                                                                  | 00b                                      | D3-       | D3+      | D2-      | D2+     | CLK- | CLK+    | D1-      | D1+       | D0-      | D0+ |

| PNSWAP     | Digital Input                  |                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                | 01b                                      | D3-       | D3+      | D0-      | D0+     | CLK- | CLK+    | D1-      | D1+       | D2-      | D2+ |

| DSWAP[1:0] | (VDDI – VSS)                   |                                                                                                                                                                                                  | -                                                                                                                                                                                                                                                | 10b                                      | D0-       | D0+      | D1-      | D1+     | CLK- | CLK+    | D2-      | D2+       | D3-      | D3+ |

|            |                                |                                                                                                                                                                                                  |                                                                                                                                                                                                                                                  | 11b                                      | D2-       | D2+      | D1-      | D1+     | CLK- | CLK+    | D0-      | D0+       | D3-      | D3+ |

|            |                                |                                                                                                                                                                                                  |                                                                                                                                                                                                                                                  | 00b                                      | D3+       | D3-      | D2+      | D2-     | CLK+ | CLK-    | D1+      | D1-       | D0+      | D0- |

|            |                                |                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                | 01b                                      | D3+       | D3-      | D0+      | D0-     | CLK+ | CLK-    | D1+      | D1-       | D2+      | D2- |

|            |                                |                                                                                                                                                                                                  |                                                                                                                                                                                                                                                  | 10b<br>11b                               | D0+       | D0-      | D1+      | D1-     | CLK+ | CLK-    | D2+      | D2-       | D3+      | D3- |

|            |                                |                                                                                                                                                                                                  |                                                                                                                                                                                                                                                  |                                          | D2+       | 02-      |          |         |      | OLK-    | 00+      | 00-       | 03+      | 03- |

| EN4PWR     | Digital Input<br>(VDDI – VSS)  |                                                                                                                                                                                                  |                                                                                                                                                                                                                                                  | Disable 4F<br>, please tie               |           |          | ction.   |         |      |         |          |           |          |     |

|         |               | - ENPWR   | - ENPWRP and ENPWRN are used to select four kind power modes for AVDD and AVEE. |                  |                           |                    |               |  |  |  |  |

|---------|---------------|-----------|---------------------------------------------------------------------------------|------------------|---------------------------|--------------------|---------------|--|--|--|--|

|         |               |           | EN4PWR ENPWRP, Power Mode Input Power<br>ENPWRN                                 |                  | AVDD                      | AVEE               |               |  |  |  |  |

| ENPWRP/ | Digital Input | N.A.      | 00                                                                              | 2-1PWR           | VDDI, VCI                 | Internal PFM       | Internal PFM  |  |  |  |  |

| ENPWRN  | (VDDI – VSS)  | N.A.      | 10                                                                              | 2-2PWR           | VDDI, AVDD                | External AVDD      | Internal PFM  |  |  |  |  |

|         |               | 0         | 11                                                                              | 3PWR             | VDDI, AVDD, AVEE          | External AVDD      | External AVEE |  |  |  |  |

|         |               | 1         | 11                                                                              | 4PWR             | VDDI, VCI, AVDD, AVEE     | External AVDD      | External AVEE |  |  |  |  |

|         |               | Note: For | more detail                                                                     | application circ | uits, please refer to NT3 | 5532 Application I | lote.         |  |  |  |  |

NEM CLOSURE

2014/07/04

#### 4.7 Analog Output for Display Driving

| Symbol                                     | Pad Type      | Description                                                                                                                                                                                         |

|--------------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCOMDC3                                    | Analog Output | - VCOMDC3 signal output for panel usage.                                                                                                                                                            |

| S1 to <mark>S3240</mark><br>and<br>SL1/SR1 | Analog Output | <ul> <li>Liquid crystal application voltage output lines.</li> <li>If source output number less than 3240, please let non-used source pins open.</li> <li>SR1 and SL1 are dummy sources.</li> </ul> |

#### 4.8 Panel Control Signals

| Symbol       | Pad Type       | Description                                        |  |  |

|--------------|----------------|----------------------------------------------------|--|--|

| CGOUTL[20:1] | Digital Output | - These pins are used for a-Si GOA control signal. |  |  |

| CGOUTR[20:1] | (VGHO – VGLO)  | - Please let non-used pins floating.               |  |  |

| MON          | JATE<br>NC     | A COME IDENT                                       |  |  |

#### 4.9 Power Supply Pins

| Symbol         | Pad Type           | Description                                                                                                                                                  |  |  |

|----------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| VDD            | LDO output         | - Power supply to the internal logic regulator circuit.                                                                                                      |  |  |

|                |                    | - Connect a capacitor to stabilize output voltage.                                                                                                           |  |  |

| AVDDR          | LDO Output         | - Positive LDO output for Driver IC usage.                                                                                                                   |  |  |

|                |                    | - Connect a capacitor to stabilize output voltage.                                                                                                           |  |  |

| AVEER          | LDO Output         | - Negative LDO output for Driver IC usage.                                                                                                                   |  |  |

|                |                    | - Connect a capacitor to stabilize output voltage.                                                                                                           |  |  |

| GVDDP          | LDO Output         | - Positive LDO output for gamma circuit.                                                                                                                     |  |  |

| GVDDN          | LDO Output         | - Negative LDO output for gamma circuit.                                                                                                                     |  |  |

| VREF           | LDO Output         | - Reference voltage output from the internal reference voltage generating circuit.                                                                           |  |  |

| VP_HSSI        | LDO Output         | - Internal logic regulator output for MIPI high speed / low power mode use.                                                                                  |  |  |

|                |                    | - Connect a capacitor for stabilization.                                                                                                                     |  |  |

| VGH            | Charge Pump Output | <ul> <li>Output voltage from the step-up circuit, and generate from AVDD, AVEE and VCL.</li> <li>Connect a capacitor to stabilize output voltage.</li> </ul> |  |  |

| C21P/C21M/     |                    | - Capacitor connection pins for the step-up circuit which generate VGH.                                                                                      |  |  |

| C22P/C22M      | Analog Output      | - If not used, please let these pins floating.                                                                                                               |  |  |

| VGL            | Charge Pump Output | - Output voltage from the step-up circuit, and generated from AVEE and VCI.                                                                                  |  |  |

| VGLOUT         |                    | - Please tie VGL with VGLOUT together.                                                                                                                       |  |  |

|                |                    | - Connect a capacitor to stabilize output voltage.                                                                                                           |  |  |

| 0<br>C31P/C31M | Analog Output      | - Capacitor connection pins for the step-up circuit which generate VGL.                                                                                      |  |  |

|                |                    | - If not used, please let these pins open.                                                                                                                   |  |  |

| VGHO           | LDO Output         | - Positive LDO output for a-Si power generator.                                                                                                              |  |  |

|                |                    | - Connect a capacitor to stabilize output voltage.                                                                                                           |  |  |

| VGLO           | LDO Output         | - Negative LDO output for a-Si power generator.                                                                                                              |  |  |

| VGLO           |                    | - Connect a capacitor to stabilize output voltage.                                                                                                           |  |  |

|                | Charge Pump Output | - Output voltage from the step-up circuit or LDO circuit, and generated from AVEE or VCI1.                                                                   |  |  |

| VCL            | Or                 | - Connect a capacitor to stabilize output voltage.                                                                                                           |  |  |

|                | LDO Output         |                                                                                                                                                              |  |  |

| C41P/C41M      | Analog Output      | - Capacitor connection pins for the step-up circuit which generate VCL.                                                                                      |  |  |

| C42P/C42M      |                    | - If not used, please let these pins floating.                                                                                                               |  |  |

| VOIA           | Charge Pump Output | - Output voltage from the step-up circuit or LDO circuit, and generated from AVDD or VCI.                                                                    |  |  |

| VCI1           | Or<br>LDO Output   | - Connect a capacitor to stabilize output voltage.                                                                                                           |  |  |

|                |                    |                                                                                                                                                              |  |  |

2014/07/04

#### 4.10 Test and Dummy Pins

| Symbol       | Pad Type                         | Description                                                                                                                                                                                                                                                                         |  |  |  |  |

|--------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| DUMMY        | DUMMY                            | <ul> <li>These pins are dummy (possess no function inside), and are not accessible to user.</li> <li>Please open these test pins.</li> </ul>                                                                                                                                        |  |  |  |  |

| COGTEST1~4   | Output                           | - Dummy pins to measure contact resistance. COGTEST1~4 pins are internal short.                                                                                                                                                                                                     |  |  |  |  |

| TEST[12:0]   | Input/Output                     | <ul> <li>Novatek internal test pins.</li> <li>Please let these pins open.</li> </ul>                                                                                                                                                                                                |  |  |  |  |

| FRM          | Input                            | - This pin is used for Novatek engineering mode.     - If not use, please tie this pin to VSS.     FRM Free Running Mode     Low Disable                                                                                                                                            |  |  |  |  |

| VDDIO        | Power Output                     | High     Enable       - This pin output a VDDI level for fixed level logic pin used.                                                                                                                                                                                                |  |  |  |  |

| VSOUT        | (VDDI – VSS)<br>Output           | <ul> <li>If not used, please let it open.</li> <li>The VSOUT pin can select to output signal type via register setting.<br/>About the detail illustration, please refer to the application notes. (CMD2 Page4, D6h ~ D8h)</li> <li>If not use, please let this pin open.</li> </ul> |  |  |  |  |

| HSOUT        | Output                           | <ul> <li>The HSOUT pin can select to output signal type via register setting.</li> <li>About the detail illustration, please refer to the application notes. (CMD2 Page4, D6h ~ D8h)</li> <li>If not use, please let this pin open.</li> </ul>                                      |  |  |  |  |

|              | Digital Output<br>(VDDI – VSS)   | <ul> <li>This pin is used for connected to the external LED driver circuit.</li> <li>It is a control signal to decrease backlight DC current in IDLE LPM mode.</li> <li>If not used, please let this pin open.</li> </ul>                                                           |  |  |  |  |

| LED_BOOST    | Digital Output<br>(VDDI – VSS)   | <ul> <li>This pin is used for connected to the external LED driver circuit.</li> <li>It is a control signal to increase backlight DC current in high brightness mode.</li> <li>If not used, please let this pin open.</li> </ul>                                                    |  |  |  |  |

| PANTE1_CTL   | Digital Output<br>(VDDI – VSS)   | - Touch panel noise reduction output signal 1.<br>- If not used, please let this pin open.                                                                                                                                                                                          |  |  |  |  |

| PANTE2_CTL   | Digital Output<br>(VDDI – VSS)   | - Touch panel noise reduction output signal 2.<br>- If not used, please let this pin open.                                                                                                                                                                                          |  |  |  |  |

| PANTE3_CTL   | Digital Oleutput<br>(VDDI – VSS) | - Touch panel noise reduction output signal 3.<br>- If not used, please let this pin open.                                                                                                                                                                                          |  |  |  |  |

| VGH1<br>VGH2 | Power Input<br>(VGHO-VSS)        | <ul> <li>This pin is used to discharge function.</li> <li>If not used, please let this pin short to VGHO.</li> </ul>                                                                                                                                                                |  |  |  |  |

| vs           | Digital Input<br>(VDDI – VSS)    | - Novatek test mode.<br>- If not used, please pull it to VSS.                                                                                                                                                                                                                       |  |  |  |  |

| нѕ           | Digital Input<br>(VDDI – VSS)    | - Novatek test mode.<br>- If not used, please pull it to VSS.                                                                                                                                                                                                                       |  |  |  |  |

| PCLK         | Digital Input<br>(VDDI – VSS)    | - Novatek test mode.<br>- if not used, please pull it to VSS.                                                                                                                                                                                                                       |  |  |  |  |

| DE           | Digital Input<br>(VDDI – VSS)    | - Novatek test mode.<br>- If not used, please pull it to VSS.                                                                                                                                                                                                                       |  |  |  |  |

| RDX          | Digital Input                    | - Novatek test mode.<br>- Please tie this pin to VDDI.                                                                                                                                                                                                                              |  |  |  |  |

#### 2014/07/04

Version 4.0

|         | (VDDI – VSS) |                                                |

|---------|--------------|------------------------------------------------|

| D[23:0] | Digital I/O  | - Novatek test mode.                           |

| D[23.0] | (VDDI – VSS) | - If not used, please let these pins floating. |

#### 4.11 Panel Test Pins

| Symbol       | Pad Type                      | Description                                                                                                                                                     |  |  |

|--------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TOP_PATEN    | Output                        | - Please let this pin open.                                                                                                                                     |  |  |

| TOP_COM      | Output                        | - Please let this pin open.                                                                                                                                     |  |  |

| BOTM_PATEN   | Output                        | - Please let this pin open.                                                                                                                                     |  |  |

| BOTM_COM     | Output                        | - Please let this pin open.                                                                                                                                     |  |  |

| DCHR1RR      | Analog ouput<br>(VGH-VSS)     | <ul> <li>For gate signal (Group 1) slope control usage. If user wants to use, please connect a resister.</li> <li>If not used, please tie it to VSS.</li> </ul> |  |  |

| DCHR2RR      | Analog ouput<br>(VGH-VSS)     | - For gate signal (Group 2) slope control usage. If user wants to use, please connect a resister.<br>- If not used, please tie it to VSS.                       |  |  |

| IMAGE_UPDATE | Digital Input<br>(VDDI - VSS) | - Image update detection input signal.<br>- If not used, please tie it to VSS.                                                                                  |  |  |

| LV_DETEC     | Digital Input<br>(VDDI – VSS) | - Low voltage detection input signal.<br>- If not used, please tie it to VSS.                                                                                   |  |  |

| U            | Ma                            |                                                                                                                                                                 |  |  |

#### 5. Function Descriptions

#### 5.1 Interfaces (SPI/I2C/MIPI)

JNP NC

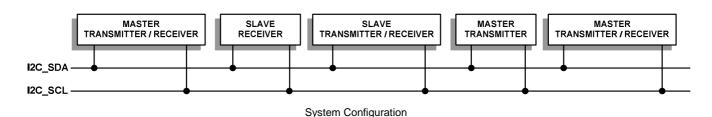

The NT35532 provides MIPI DSI, MIPI DSI + SPI (8/9-bits) and MIPI DSI + I2C interface. The interface can be determined by hardware pins (IM[2:0]). When MIPI DSI + SPI (8/9-bits) and MIPI DSI + I2C interface, SPI (8/9-bits) and I2C only support register access. Besides, user also can read and write registers via MIPI interface. But NT35532 doesn't support these two I/F to access register simultaneously. NT35532 also provides another multi-interface selection by register setting (CMD1 F3h), It is only available when IM[2:0] = 110b.

| IM2 | IM1 | IMO | System Interface                                          | Data Pins                                            | Available Colors  |

|-----|-----|-----|-----------------------------------------------------------|------------------------------------------------------|-------------------|

| 0   | 0   | 0   | MIPI DSI + I2C                                            | MIPI : HSSI_D0_P/N ~ HSSI_D3_P/N<br>I2C : I2C_SDA    | 65k, 262k, 16.77M |

| 0   | 0   | 1   | Reserved                                                  | Reserved                                             | Reserved          |

| 0   | 1   | 0   | MIPI DSI + SPI (9-bits Type)<br>(SCL rising edge trigger) | MIPI : HSSI_D0_P/N ~ HSSI_D3_P/N<br>SPI : SDI, SDO   | 65k, 262k, 16.77M |

| 0   | 1   | 1   | MIPI DSI + SPI (8-bits Type)<br>(SCL rising edge trigger) | MIPI : HSSI_D0_P/N ~ HSSI_D3_P/N<br>SPI : SDI, SDO   | 65k, 262k, 16.77M |