Ph. 480-503-4295 | NOPP@FocusLCD.com

## TFT | CHARACTER | UWVD | FSC | SEGMENT | CUSTOM | REPLACEMENT

## **Character Display Module**

## Part Number

C81BLGFKN06WN50XAG

#### Overview

Character: 8x1(55x27.6), FSTN, Black background, No Backlight, Bottom view, Wide temp, Transmissive (negative), 5V LCD, Controller=ST7036I, RoHS Compliant

## 1.Features

- 1. 5x8 dots with cursor

- 2. Built-in controller ST7036

- 3. +3.3V power supply

- 4. 1/8 duty cycle;1/4bias5. 8characters \*1lines display

|                   | □TN               |         |                              |             |  |  |  |

|-------------------|-------------------|---------|------------------------------|-------------|--|--|--|

| LCD type          | □FSTN             | ☑FSTN N |                              |             |  |  |  |

|                   | □STN Yellow Green |         | □STN Gray □STN Blue Negative |             |  |  |  |

| View direction    | ☑6 O'clock        |         | □12 O'clock                  |             |  |  |  |

| Rear Polarizer    | □Reflective       |         | □Transflective ☑Transmissive |             |  |  |  |

| Temperature Range | □Normal           |         | ☑Wide                        | □Super Wide |  |  |  |

| DC to DC circuit  | □Build-in         |         | ☑Not Build-in                |             |  |  |  |

| Touch screen      | □With             |         | ☑Without                     |             |  |  |  |

| Font type         | ☑English-Japanese |         | □English-Europen             | □Other      |  |  |  |

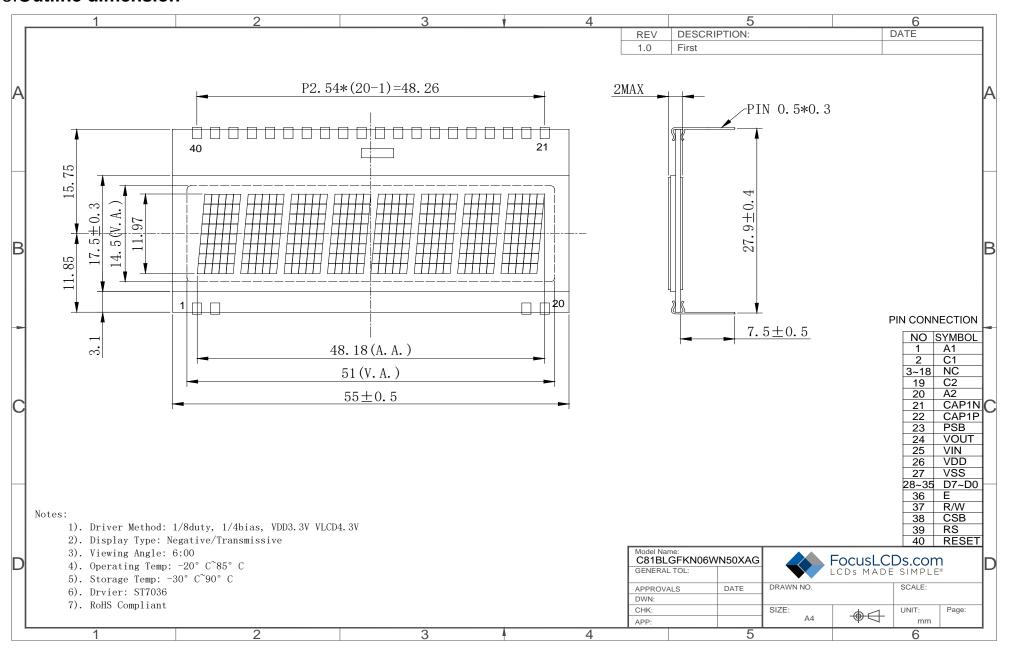

## 2. MECHANICAL SPECIFICATIONS

| Module size  | 55.0mm(L)*27.6mm(W)*9.2mm(H) |

|--------------|------------------------------|

| Viewing area | 51.0mm(L)*14.5mm(W)          |

| Weight       | Approx.                      |

### 3. Outline dimension

3

www.FocusLCDs.com

## 4. Absolute maximum ratings

| Item                        | Symbol                           |     | Standard |     | Unit |

|-----------------------------|----------------------------------|-----|----------|-----|------|

| Power voltage               | V <sub>DD</sub> -V <sub>SS</sub> | 0   | -        | 7.0 | M    |

| Input voltage               | Vin                              | VSS | -        | VDD | V    |

| Operating temperature range | Vop                              | -10 | -        | +50 | °C   |

| Storage temperature range   | Vst                              | -20 | -        | +70 | C    |

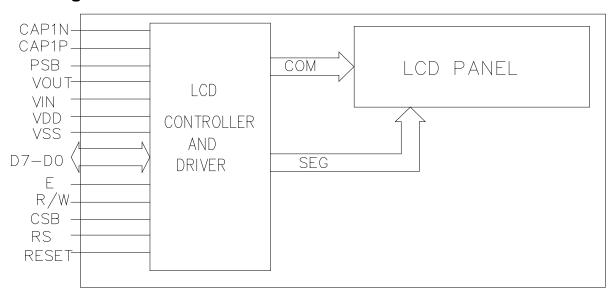

## 5.Block diagram

## 6.Interface pin description

| Pin no. | Symbol | External connection | Function                                          |

|---------|--------|---------------------|---------------------------------------------------|

| 1       | A1     | Power supply        | Power supply (+3.0V) for BKL                      |

| 2       | C1     | Power supply        | Ground for BKL (GND)                              |

| 3~18    | NC     |                     |                                                   |

| 19      | C2     | Power supply        | Ground for BKL (GND)                              |

| 20      | A2     | Power supply        | Power supply (+3.0V) for BKL                      |

| 21      | CAP1N  | Power supply        | For voltage booster circuit                       |

| 22      | CAP1P  | Power supply        | For voltage booster circuit                       |

| 23      | PSB    | MPU                 | Interface selection                               |

| 24      | VOUT   | Power supply        | DC/DC voltage converter                           |

| 25      | VIN    | Power supply        | Input the voltage to booster                      |

| 26      | VDD    | Power supply        | Power supply (+3.3V) for LCM                      |

| 27      | VSS    | Power supply        | Signal ground for LCM (GND)                       |

| 28~35   | D7-D0  | MPU                 | This is an 8-bit-directional data bus.            |

| 36      | Е      | MPU                 | Operation (data read/write) enable signal         |

| 37      | R/W    | MPU                 | Read/write select signal                          |

| 38      | CSB    | MPU                 | Chip select in parallel mode and serial interface |

| 39      | RS     | MPU                 | Register select signal                            |

| 40      | RESET  | MPU                 | External reset PIN                                |

## 7. Optical characteristics

FSTN type display module (Ta=25°C, VDD=3.3V)

| Item            |           | Symbol     | Condition | Min. | Тур. | Max. | Unit  |  |

|-----------------|-----------|------------|-----------|------|------|------|-------|--|

| Viewing angle   | LeftRight | θ          | Ta=25℃    | -    | 60   | -    | 400   |  |

| (6 0'clock)     | TopBottom | opBottom θ |           | -    | 70   | -    | deg   |  |

| Contrast ratio  |           | CR         |           | 3    | 5    | -    | -     |  |

| Doon on oo time | Rise      | <b>t</b> r | Ta=25℃    | -    | 150  | 250  | 100.0 |  |

| Response time   | Tall      | <b>t</b> f |           | -    | 200  | 300  | ms    |  |

## 8. Electrical characteristics

DC characteristics

| Parameter                | Symbol           | Conditions                    | Min. | Тур. | Max.            | Unit |

|--------------------------|------------------|-------------------------------|------|------|-----------------|------|

| Supply voltage for LCD   | $V_{DD}$ - $V_0$ | Ta =25°C                      | -    | 4.3  | -               | V    |

| Input voltage            | $V_{DD}$         |                               | -    | 3.3  | -               |      |

| Supply current           | I <sub>DD</sub>  | Ta=25℃, V <sub>DD</sub> =3.3V | -    | 1.0  | 1.5             | mA   |

| Input leakage current    | ILKG             |                               | -    | -    | 1.0             | uA   |

| "H" level input voltage  | VIH              |                               | 2.2  | -    | V <sub>DD</sub> |      |

| "L" level input voltage  | VIL              | Twice initial value or less   | 0    | -    | 0.6             | V    |

| "H" level output voltage | Vон              | LOH=-0.25mA                   | 2.4  | -    | -               | V    |

| "L" level output voltage | Vol              | LOH=1.6mA                     | -    | -    | 0.4             |      |

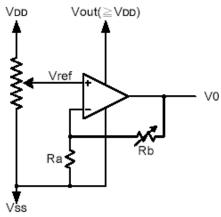

## 9.Contrast adjust

## V0 voltage follower value calculation

V0=(1+

$$\frac{\text{Rb}}{\text{Ra}}$$

) × Vref

While Vref=VDD ×(  $\frac{\alpha+36}{100}$  )

| C5 | C4 | C3 | C2 | C1 | C0 | α  |

|----|----|----|----|----|----|----|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 0  | 0  | 0  | 0  | 0  | 1  | 1  |

| 0  | 0  | 0  | 0  | 1  | 0  | 2  |

|    |    |    | :  |    |    | :  |

|    |    |    | :  |    |    | :  |

| 1  | 1  | 1  | 1  | 0  | 1  | 61 |

| 1  | 1  | 1  | 1  | 1  | 0  | 62 |

| 1  | 1  | 1  | 1  | 1  | 1  | 63 |

| Rab2 | Rab1 | Rab0 | 1+Rb/Ra |

|------|------|------|---------|

| 0    | 0    | 0    | 1       |

| 0    | 0    | 1    | 1.25    |

| 0    | 1    | 0    | 1.5     |

| 0    | 1    | 1    | 1.8     |

| 1    | 0    | 0    | 2       |

| 1    | 0    | 1    | 2.5     |

| 1    | 1    | 0    | 3       |

| 1    | 1    | 1    | 3.75    |

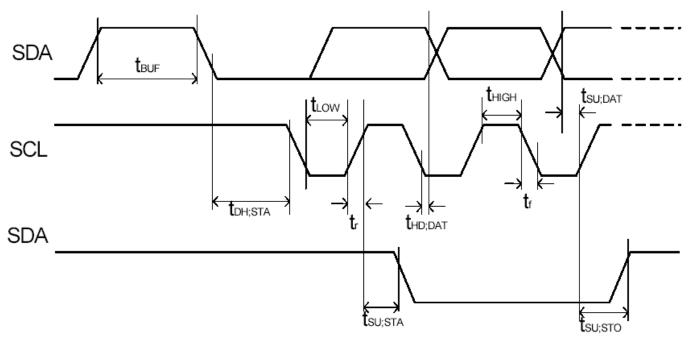

## **10.Timing Characteristics**

( Ta = 25°C )

| Item                                             | Signal <sub>i</sub> Symbol <sub>i</sub> Condition |                     |            | VDD=2.7<br>Rati      |      | VDD=4.5<br>Rati      | Units |      |

|--------------------------------------------------|---------------------------------------------------|---------------------|------------|----------------------|------|----------------------|-------|------|

| item                                             | Sigilal                                           | Cyllibol            | Contaition | Min.                 | Max. | Min.                 | Max.  | Omes |

| SCL clock frequency                              |                                                   | f <sub>SCLK</sub>   |            | DC                   | 300K | DC                   | 400   | kHz  |

| SCL clock low period                             | SCL                                               | $t_{LOW}$           | _          | 2.5                  |      | 1.3                  |       |      |

| SCL clock high period                            |                                                   | t <sub>HIGH</sub>   |            | 0.6                  | -    | 0.6                  |       | μs   |

| Data set-up time                                 | SDA                                               | t <sub>SU;DAT</sub> |            | 1800                 | _    | 700                  | _     | ns   |

| Data hold time                                   | SDA                                               | t <sub>HD:DAT</sub> | _          | 0                    | 0.5  | 0                    | 0.5   | μs   |

| SCL,SDA rise time                                | SCL,                                              | t <sub>r</sub>      |            | 20+0.1C <sub>b</sub> | 300  | 20+0.1C <sub>b</sub> | 300   | ns   |

| SCL,SDA fall time                                | SDA t <sub>f</sub>                                |                     | 1 -        | 20+0.1C <sub>b</sub> | 300  | 20+0.1C <sub>b</sub> | 300   | 1115 |

| Capacitive load represent by each bus line       |                                                   | Сь                  | _          | _                    | 400  | _                    | 400   | pf   |

| Setup time for a repeated START condition        | SDA                                               | t <sub>SU;STA</sub> | _          | 0.6                  |      | 0.6                  | _     | μs   |

| Start condition hold time                        |                                                   | t <sub>HD;STA</sub> | _          | 1.8                  |      | 1.0                  |       | μs   |

| Setup time for STOP condition                    |                                                   | t <sub>su;sto</sub> | _          | 0.6                  |      | 0.6                  | _     | μs   |

| Bus free time between a Stop and START condition | SCL                                               | t <sub>BUF</sub>    | _          | 1.3                  | _    | 1.3                  | _     | μs   |

### **I2C** interface

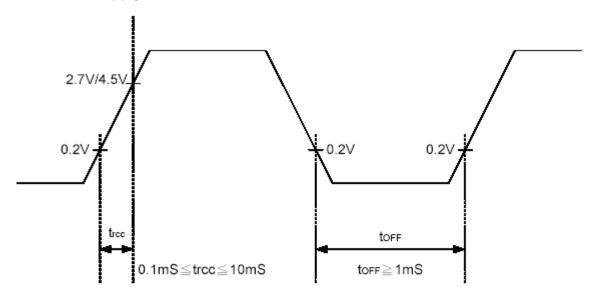

### Internal Power Supply Reset

#### Notes:

- toff compensates for the power oscillation period caused by momentary power supply oscillations.

- Specified at 4.5V for 5V operation, and at 2.7V for 3V operation.

- For if 2.7V/4.5V is not reached during 3V/5V operation, internal reset circuit will not operate normally.

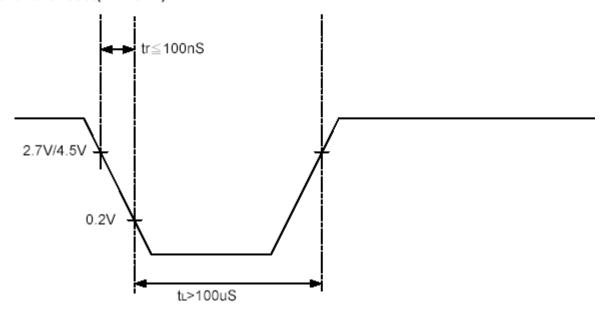

#### Hardware reset(XRESET)

#### System Interface

This chip has all four kinds of interface type with MPU: 4-bit bus, 8-bit bus, serial and fast I<sup>2</sup>C interface. 4-bit bus or 8-bit bus is selected by DL bit in the instruction register.

During read or write operation, two 8-bit registers are used. One is data register (DR), the other is instruction register(IR).

The data register(DR) is used as temporary data storage place for being written into or read from DDRAM/CGRAM/ICON RAM, target RAM is selected by RAM address setting instruction. Each internal operation, reading from or writing into RAM, is done automatically. So to speak, after MPU reads DR data, the data in the next DDRAM/CGRAM/ICON RAM address is transferred into DR automatically. Also after MPU writes data to DR, the data in DR is transferred into DDRAM/CGRAM/ICON RAM automatically.

The Instruction register(IR) is used only to store instruction code transferred from MPU. MPU cannot use it to read instruction data.

To select register, use RS input pin in 4-bit/8-bit bus mode.

| RS | R/W | Operation                                                         |  |  |  |  |  |  |  |  |  |

|----|-----|-------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| L  | L   | Instruction Write operation (MPU writes Instruction code into IR) |  |  |  |  |  |  |  |  |  |

| L  | Н   | Read Busy Flag(DB7) and address counter (DB0 ~ DB6)               |  |  |  |  |  |  |  |  |  |

| Н  | L   | Data Write operation (MPU writes data into DR)                    |  |  |  |  |  |  |  |  |  |

| Н  | Н   | Data Read operation (MPU reads data from DR)                      |  |  |  |  |  |  |  |  |  |

Table 1. Various kinds of operations according to RS and R/W bits.

#### I<sup>2</sup>C interface

It just only could write Data or Instruction to ST7036 by the IIC Interface. It could not read Data or Instruction from ST7036 (except Acknowledge signal).

SCL: serial clock input SDA IN: serial data input

SDA OUT: acknowledge response output

Slaver address could set from "0111100" to "0111111".

The I<sup>2</sup>C interface send RAM data and executes the commands sent via the I<sup>2</sup>C Interface. It could send data in to the RAM. The I<sup>2</sup>C Interface is two-line communication between different ICs or modules. The two lines are a Serial Data line (SDA) and a Serial Clock line (SCL). Both lines must be connected to a positive supply via a pull-up resistor. Data transfer may be initiated only when the bus is not busy.

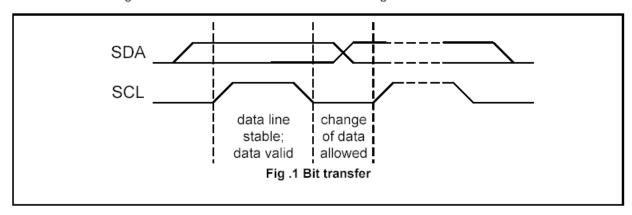

#### BIT TRANSFER

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the HIGH period of the clock pulse because changes in the data line at this time will be interpreted as a control signal. Bit transfer is illustrated in Fig.1.

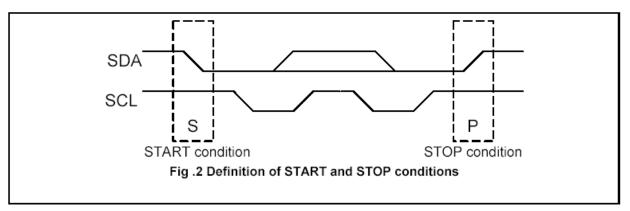

#### START AND STOP CONDITIONS

Both data and clock lines remain HIGH when the bus is not busy. A HIGH-to-LOW transition of the data line, while the clock is HIGH is defined as the START condition (S). A LOW-to-HIGH transition of the data line while the clock is HIGH is defined as the STOP condition (P). The START and STOP conditions are illustrated in Fig.2.

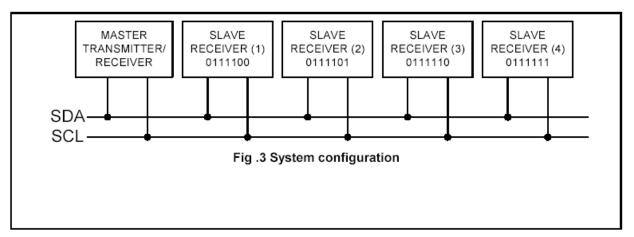

#### SYSTEM CONFIGURATION

The system configuration is illustrated in Fig.3.

- · Transmitter: the device, which sends the data to the bus

- · Master: the device, which initiates a transfer, generates clock signals and terminates a transfer

- · Slave: the device addressed by a master

- · Multi-Master: more than one master can attempt to control the bus at the same time without corrupting the message

- · Arbitration: procedure to ensure that, if more than one master simultaneously tries to control the bus, only one is allowed to so and the message is not corrupted

- · Synchronization: procedure to synchronize the clock signals of two or more devices.

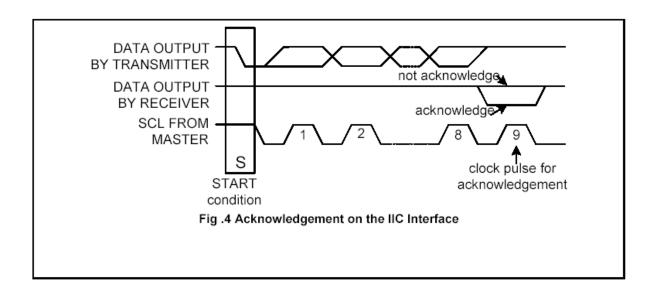

#### **ACKNOWLEDGE**

#### Acknowledge signal (ACK) is not BF signal in parallel interface.

Each byte of eight bits is followed by an acknowledge bit. The acknowledge bit is a HIGH signal put on the bus by the transmitter during which time the master generates an extra acknowledge related clock pulse. A slave receiver which is addressed must generate an acknowledge after the reception of each byte. A master receiver must also generate an acknowledge after the reception of each byte that has been clocked out of the slave transmitter. The device that acknowledges must pull-down the SDA line during the acknowledge clock pulse, so that the SDA line is stable LOW durir the HIGH period of the acknowledge related clock pulse (set-up and hold times must be taken into consideration). A master receiver must signal an end-of-data to the transmitter by not generating an acknowledge on the last byte that has been clocked out of the slave. In this event the transmitter must leave the data line HIGH to enable the master to generate a STO condition. Acknowledgement on the I<sup>2</sup>C Interface is illustrated in Fig.4.

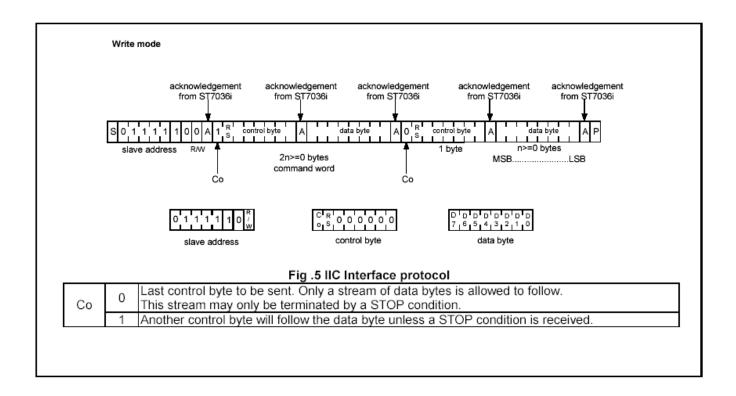

#### I<sup>2</sup>C Interface protocol

The ST7036 supports command, data write addressed slaves on the bus.

Before any data is transmitted on the I<sup>2</sup>C Interface, the device, which should respond, is addressed first. Four 7-bit slave addresses (0111100 to 0111111) are reserved for the ST7036. The R/W is assigned to 0 for Write only. The I<sup>2</sup>C Interface protocol is illustrated in Fig.5.

The sequence is initiated with a START condition (S) from the I<sup>2</sup>C Interface master, which is followed by the slave address. All slaves with the corresponding address acknowledge in parallel, all the others will ignore the I<sup>2</sup>C Interface transfer. After acknowledgement, one or more command words follow which define the status of the addressed slaves.

A command word consists of a control byte, which defines Co and RS, plus a data byte.

The last control byte is tagged with a cleared most significant bit (i.e. the continuation bit Co). After a control byte with a cleared Co bit, only data bytes will follow. The state of the RS bit defines whether the data byte is interpreted as a command or as RAM data. All addressed slaves on the bus also acknowledge the control and data bytes. After the last control byte, depending on the RS bit setting; either a series of display data bytes or command data bytes may follow. If the RS bit is set to logic 1, these display bytes are stored in the display RAM at the address specified by the data pointer. The data pointer is automatically updated and the data is directed to the intended ST7036i device. If the RS bit of the last control byte is set to logic 0, these command bytes will be decoded and the setting of the device will be changed according to the received commands. Only the addressed slave makes the acknowledgement after each byte. At the end of the transmission the I<sup>2</sup>C INTERFACE-bus master issues a STOP condition (P).

During write operation, two 8-bit registers are used. One is data register (DR), the other is instruction register(IR).

The data register(DR) is used as temporary data storage place for being written into DDRAM/CGRAM/ICON RAM, target RAM is selected by RAM address setting instruction. Each internal operation, writing into RAM, is done automatically. So to speak, after MPU writes data to DR, the data in DR is transferred into DDRAM/CGRAM/ICON RAM automatically.

The Instruction register(IR) is used only to store instruction code transferred from MPU. MPU cannot use it to read instruction data.

To select register, use RS bit input in IIC interface.

| RS | R/W | Operation                                                         |

|----|-----|-------------------------------------------------------------------|

| L  | L   | Instruction Write operation (MPU writes Instruction code into IR) |

| Н  | L   | Data Write operation (MPU writes data into DR)                    |

Table 2. Various kinds of operations according to RS and R/W bits.

#### Busy Flag (BF)

When BF = "High", it indicates that the internal operation is being processed. So during this time the next instruction cannot be accepted. BF can be read, when RS = Low and R/W = High (Read Instruction Operation), through DB7 port. Before executing the next instruction, be sure that BF is not High.

#### Address Counter (AC)

Address Counter(AC) stores DDRAM/CGRAM/ICON RAM address, transferred from IR. After writing into (reading from) DDRAM/CGRAM/ICON RAM, AC is automatically increased (decreased) by 1. When RS = "Low" and R/W = "High", AC can be read through DB0 ~ DB6 ports.

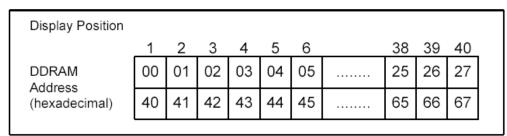

#### Display Data RAM (DDRAM)

Display data RAM (DDRAM) stores display data represented in 8-bit character codes. Its extended capacity is 80 x 8 bits, or 80 characters. The area in display data RAM (DDRAM) that is not used for display can be used as general data RAM. See Figure 6 for the relationships between DDRAM addresses and positions on the liquid crystal display.

The DDRAM address (ADD) is set in the address counter (AC) as hexadecimal.

### > 2-line display (N3=0,N = 1) (Figure 9)

Case 1: When the number of display characters is less than  $40 \times 2$  lines, the two lines are displayed from the head. Note that the first line end address and the second line start address are not consecutive. For example, when just the ST7036 is used, 20 characters  $\times$  2 lines are displayed. See Figure 9. When display shift operation is performed, the DDRAM address shifts. See Figure 10.

Fig. 9 2-Line Display

| Display<br>Position | 1  | 2  | 3    | 4     | 5    | 6     | 7     | 8     |                   | 17 | 18 | 19 | 20 |

|---------------------|----|----|------|-------|------|-------|-------|-------|-------------------|----|----|----|----|

| DDRAM               | 00 | 01 | 02   | 03    | 04   | 05    | 06    | 07    |                   | 10 | 11 | 12 | 13 |

| Address             | 40 | 41 | 42   | 43    | 44   | 45    | 46    | 47    |                   | 50 | 51 | 52 | 53 |

|                     |    |    |      |       |      |       |       |       |                   |    |    |    |    |

| For Shift           | 01 | 02 | 03   | 04    | 05   | 06    | 07    | 08    |                   | 11 | 12 | 13 | 14 |

| Left                | 41 | 42 | 43   | 44    | 45   | 46    | 47    | 48    |                   | 51 | 52 | 53 | 54 |

|                     |    |    | •    |       |      |       |       |       |                   |    |    | •  |    |

| For Shift           | 27 | 00 | 01   | 02    | 03   | 04    | 05    | 06    |                   | 0F | 10 | 11 | 12 |

| Right               | 67 | 40 | 41   | 42    | 43   | 44    | 45    | 46    |                   | 4F | 50 | 51 | 52 |

|                     |    |    | Fia. | 10 2- | Line | bv 20 | )-Cha | racte | r Displav Example |    |    |    |    |

#### Character Generator ROM (CGROM)

The character generator ROM generates  $5 \times 8$  dot character patterns from 8-bit character codes. It can generate  $240/250/248/256 \ 5 \times 8$  dot character patterns (select by OPR1/2 ITO pin). User-defined character patterns are also available by mask-programmed ROM.

#### Character Generator RAM (CGRAM)

In the character generator RAM, the user can rewrite character patterns by program. For 5 x 8 dots, eight character patterns can be written.

Write into DDRAM the character codes at the addresses shown as the left column of Table 5 to show the character patterns stored in CGRAM.

See Table 5 for the relationship between CGRAM addresses and data and display patterns. Areas that are not used for display can be used as general data RAM.

|    |    |    |    |    | Coc<br>ata |    |    |    |    | CGF<br>\dd |    |    |    |    |    |    | cte<br>RA |    |    |    | ;  |

|----|----|----|----|----|------------|----|----|----|----|------------|----|----|----|----|----|----|-----------|----|----|----|----|

| b7 | b6 | b5 | b4 | b3 | b2         | b1 | bO | b5 | b4 | b3         | b2 | b1 | b0 | b7 | b6 | b5 | b4        | b3 | b2 | b1 | b0 |

|    |    |    |    |    | 0          | 0  | 0  |    |    |            | 0  | 0  | 0  |    |    |    | 1         | 1  | 1  | 1  | 1  |

|    |    |    |    |    | 0          | 0  | 0  |    |    |            | 0  | 0  | 1  |    |    |    | 0         | 0  | 1  | 0  | 0  |

|    |    |    |    |    | 0          | 0  | 0  |    |    |            | 0  | 1  | 0  |    |    |    | 0         | 0  | 1  | 0  | 0  |

| 0  | 0  | 0  | 0  | _  | 0          | 0  | 0  | 0  | 0  | 0          | 0  | 1  | 1  | _  | _  | _  | 0         | 0  | 1  | 0  | 0  |

| Ŭ  | ľ  | 0  | 0  |    | 0          | 0  | 0  |    | 0  |            | 1  | 0  | 0  |    |    |    | 0         | 0  | 1  | 0  | 0  |

|    |    |    |    |    | 0          | 0  | 0  |    |    |            | 1  | 0  | 1  |    |    |    | 0         | 0  | 1  | 0  | 0  |

|    |    |    |    |    | 0          | 0  | 0  |    |    |            | 1  | 1  | 0  |    |    |    | 0         | 0  | 1  | 0  | 0  |

|    |    |    |    |    | 0          | 0  | 0  |    |    |            | 1  | 1  | 1  |    |    |    | 0         | 0  | 0  | 0  | 0  |

|    |    |    |    |    | 0          | 0  | 1  |    |    |            | 0  | 0  | 0  |    |    |    | 1         | 1  | 1  | 1  | 0  |

|    |    |    |    |    | 0          | 0  | 1  |    |    |            | 0  | 0  | 1  |    |    |    | 1         | 0  | 0  | 0  | 1  |

|    |    |    |    |    | 0          | 0  | 1  |    |    |            | 0  | 1  | 0  |    |    |    | 1         | 0  | 0  | 0  | 1  |

| 0  | 0  | 0  | 0  | _  | 0          | 0  | 1  | 0  | 0  | 1          | 0  | 1  | 1  | _  | _  | _  | 1         | 1  | 1  | 1  | 0  |

| Ŭ  | ľ  | 0  | 0  |    | 0          | 0  | 1  |    | 0  |            | 1  | 0  | 0  |    |    |    | 1         | 0  | 1  | 0  | 0  |

|    |    |    |    |    | 0          | 0  | 1  |    |    |            | 1  | 0  | 1  |    |    |    | 1         | 0  | 0  | 1  | 0  |

|    |    |    |    |    | 0          | 0  | 1  |    |    |            | 1  | 1  | 0  |    |    |    | 1         | 0  | 0  | 0  | 1  |

|    |    |    |    |    | 0          | 0  | 1  |    |    |            | 1  | 1  | 1  |    |    |    | 0         | 0  | 0  | 0  | 0  |

Table 5 Relationship between CGRAM Addresses, Character Codes (DDRAM) and Character patterns (CGRAM Data)

#### Notes:

- Character code bits 0 to 2 correspond to CGRAM address bits 3 to 5 (3 bits: 8 types).

- 2. CGRAM address bits 0 to 2 designate the character pattern line position. The 8th line is the cursor position and its display is formed by a logical OR with the cursor. Maintain the 8th line data, corresponding to the cursor display position, at 0 as the cursor display. If the 8th line data is 1, 1 bits will light up the 8th line regardless of the cursor presence.

- 3. Character pattern row positions correspond to CGRAM data bits 0 to 4 (bit 4 being at the left).

- 4. As shown Table 5, CGRAM character patterns are selected when character code bits 4 to 7 are all 0. However, since character code bit 3 has no effect, the R display example above can be selected by either character code 00H or 08H.

- 5. "1" for CGRAM data corresponds to display selection and "0" to non-selection, "-" Indicates no effect.

- 6. Different OPR1/2 ITO option can select different CGRAM size.

## 11.Instruction description

There are four categories of instructions that:

- Designate ST7036 functions, such as display format, data length, etc.

- Set internal RAM addresses

- Perform data transfer with internal RAM

- Others

#### > instruction table at "Normal mode"

(when "EXT" option pin connect to VDD, the instruction set follow below table)

| Instruction                      |    |     |     |     | ucti |     |     |     |          |     | Description                                                                                                                               |                | nstructio<br>ecution T |                |

|----------------------------------|----|-----|-----|-----|------|-----|-----|-----|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------|----------------|

| instruction                      | RS | R/W | DB7 | DB6 | DB5  | DB4 | DB3 | DB2 | DB1      | DB0 | Description                                                                                                                               | OSC=<br>380kHz | OSC=<br>540kHz         | OSC=<br>700kHz |

| Clear<br>Display                 | 0  | 0   | 0   | 0   | 0    | 0   | 0   | 0   | 0        | 1   | Write "20H" to DDRAM. and set DDRAM address to "00H" from AC                                                                              | 1.08<br>ms     | 0.76<br>ms             | 0.59<br>ms     |

| Return<br>Home                   | 0  | 0   | 0   | 0   | 0    | 0   | 0   | 0   | 1        | ×   | Set DDRAM address to "00H" from<br>AC and return cursor to its original<br>position if shifted. The contents of<br>DDRAM are not changed. | 1.08<br>ms     | 0.76<br>ms             | 0.59<br>ms     |

| Entry Mode<br>Set                | 0  | 0   | 0   | 0   | 0    | 0   | 0   | 1   | <u> </u> | Ø   | Sets cursor move direction and<br>specifies display shift. These<br>operations are performed during<br>data write and read.               | 26.3 µs        | 18.5 µs                | 14.3 µs        |

| Display<br>ON/OFF                | 0  | 0   | 0   | 0   | 0    | 0   | 1   | D   | O        | В   | D=1:entire display on<br>C=1:cursor on<br>B=1:cursor position on                                                                          | 26.3 µs        | 18.5 µs                | 14.3 µs        |

| Cursor or<br>Display Shift       | 0  | 0   | 0   | 0   | 0    | 1   | S/C | R/L | ×        | ×   | S/C and R/L:<br>Set cursor moving and display shift<br>control bit, and the direction, without<br>changing DDRAM data.                    | 26.3 µs        | 18.5 µs                | 14.3 µs        |

| Function Set                     | 0  | 0   | 0   | 0   | 1    | DL  | N   | х   | Х        | Х   | DL: interface data is 8/4 bits<br>N: number of line is 2/1                                                                                | 26.3 µs        | 18.5 µs                | 14.3 µs        |

| Set CGRAM                        | 0  | 0   | 0   | 1   | AC5  | AC4 | AC3 | AC2 | AC1      | AC0 | Set CGRAM address in address counter                                                                                                      | 26.3 µs        | 18.5 µs                | 14.3 µs        |

| Set DDRAM<br>Address             | 0  | 0   | 1   | AC6 | AC5  | AC4 | AC3 | AC2 | AC1      | AC0 | Set DDRAM address in address counter                                                                                                      | 26.3 µs        | 18.5 µs                | 14.3 µs        |

| Read Busy<br>Flag and<br>Address | 0  | 1   | BF  | AC6 | AC5  | AC4 | AC3 | AC2 | AC1      | AC0 | Whether during internal operation or<br>not can be known by reading BF.<br>The contents of address counter<br>can also be read.           | 0              | 0                      | 0              |

| Write Data<br>to RAM             | 1  | 0   | D7  | D6  | D5   | D4  | D3  | D2  | D1       | D0  | Write data into internal RAM<br>(DDRAM/CGRAM)                                                                                             | 26.3 μs        | 18.5 µs                | 14.3 µs        |

| Read Data<br>from RAM            | 1  | 1   | D7  | D6  | D5   | D4  | D3  | D2  | D1       | D0  | Read data from internal RAM<br>(DDRAM/CGRAM)                                                                                              | 26.3 µs        | 18.5 µs                | 14.3 µs        |

#### Note

Be sure the ST7036 is not in the busy state (BF = 0) before sending an instruction from the MPU to the ST7036. If an instruction is sent without checking the busy flag, the time between the first instruction and next instruction will take much longer than the instruction time itself. Refer to Instruction Table for the list of each instruction execution time.

## > instruction table at "Extension mode"

(when "EXT" option pin connect to Vss, the instruction set follow below table)

| (WHOTI EXT                       | Opti | on p |     |      |      |     |     |     | aout | 1130 | t follow below table)                                                                                                            | 1.             | nstructio      | \n             |

|----------------------------------|------|------|-----|------|------|-----|-----|-----|------|------|----------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|----------------|

| Instruction                      |      |      | lr  | nstr | ucti | on  | Coc | de  |      |      | Description                                                                                                                      |                | cution T       |                |

| mstraction                       | RS   | R/W  | DB7 | DB6  | DB5  | DB4 | DB3 | DB2 | DB1  | DB0  | •                                                                                                                                | OSC=<br>380kHz | OSC=<br>540kHz | OSC=<br>700kHz |

| Clear<br>Display                 | 0    | 0    | 0   | 0    | 0    | 0   | 0   | 0   | 0    | 1    | Write "20H" to DDRAM. and set DDRAM address to "00H" from AC                                                                     | 1.08<br>ms     | 0.76<br>ms     | 0.59<br>ms     |

| Return<br>Home                   | 0    | 0    | 0   | 0    | 0    | 0   | 0   | 0   | 1    | х    | Set DDRAM address to "00H" from AC and return cursor to its original position if shifted. The contents of DDRAM are not changed. | 1.08<br>ms     | 0.76<br>ms     | 0.59<br>ms     |

| Entry Mode<br>Set                | 0    | 0    | 0   | 0    | 0    | 0   | 0   | 1   | I/D  | S    | Sets cursor move direction and<br>specifies display shift. These<br>operations are performed during<br>data write and read.      | 26.3 µs        | 18.5 µs        | 14.3 µs        |

| Display<br>ON/OFF                | 0    | 0    | 0   | 0    | 0    | 0   | 1   | D   | С    | В    | D=1:entire display on<br>C=1:cursor on<br>B=1:cursor position on                                                                 | 26.3 μs        | 18.5 µs        | 14.3 µs        |

| Function Set                     | 0    | 0    | 0   | 0    | 1    | DL  | Z   | DH  | IS2  | IS1  | DL: interface data is 8/4 bits<br>N: number of line is 2/1<br>DH: double height font<br>IS[2:1]: instruction table select        | 26.3 µs        | 18.5 µs        | 14.3 µs        |

| Set DDRAM<br>Address             | 0    | 0    | 1   | AC6  | AC5  | AC4 | AC3 | AC2 | AC1  | AC0  | Set DDRAM address in address counter                                                                                             | 26.3 µs        | 18.5 µs        | 14.3 μs        |

| Read Busy<br>Flag and<br>Address | 0    | 1    | BF  | AC6  | AC5  | AC4 | AC3 | AC2 | AC1  | AC0  | Whether during internal operation or<br>not can be known by reading BF.<br>The contents of address counter<br>can also be read.  | 0              | 0              | 0              |

| Write Data<br>to RAM             | 1    | 0    | D7  | D6   | D5   | D4  | D3  | D2  | D1   | D0   | Write data into internal RAM<br>(DDRAM/CGRAM/ICONRAM)                                                                            | 26.3 μs        | 18.5 µs        | 14.3 µs        |

| Read Data<br>from RAM            | 1    | 1    | D7  | D6   | D5   | D4  | D3  | D2  | D1   | D0   | Read data from internal RAM<br>(DDRAM/CGRAM/ICONRAM)                                                                             | 26.3 μs        | 18.5 µs        | 14.3 µs        |

|                            |   |   |   |   |     | Inst | truc | tior | ı ta | ble | 0(IS[2:1]=[0,0])                                                                                                       |         |         |         |

|----------------------------|---|---|---|---|-----|------|------|------|------|-----|------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|

| Cursor or<br>Display Shift | 0 | 0 | 0 | 0 | 0   | 1    | S/C  | R/L  | X    | Х   | S/C and R/L:<br>Set cursor moving and display shift<br>control bit, and the direction, without<br>changing DDRAM data. | 26.3 µs | 18.5 µs | 14.3 µs |

| Set CGRAM                  | 0 | 0 | 0 | 1 | AC5 | AC4  | AC3  | AC2  | AC1  | AC0 | Set CGRAM address in address counter                                                                                   | 26.3 μs | 18.5 µs | 14.3 µs |

|                                        |   |   |   |   |   | Inst | truc | tior     | ı ta     | ble      | 1(IS[2:1]=[0,1])                                                                                                  |         |         |         |

|----------------------------------------|---|---|---|---|---|------|------|----------|----------|----------|-------------------------------------------------------------------------------------------------------------------|---------|---------|---------|

| Bias Set                               | 0 | 0 | 0 | 0 | 0 | 1    | BS   | 1        | 0        | FX       | BS=1:1/4 bias BS=0:1/5 bias FX: fixed on high in 3-line application and fixed on low in other applications.       | _       | 18.5 µs | 14.3 µs |

| Set ICON<br>Address                    | 0 | 0 | 0 | 1 | 0 | 0    | AC3  | AC2      | AC1      | AC0      | Set ICON address in address counter.                                                                              | 26.3 µs | 18.5 µs | 14.3 µs |

| Power/ICON<br>Control/<br>Contrast Set | 0 | 0 | 0 | 1 | 0 | 1    | lon  | Bon      | C5       | C4       | Ion: ICON display on/off<br>Bon: set booster circuit on/off<br>C5,C4: Contrast set for internal<br>follower mode. | 26.3 µs | 18.5 µs | 14.3 µs |

| Follower<br>Control                    | 0 | 0 | 0 | 1 | 1 | 0    | Fon  | Rab<br>2 | Rab<br>1 | Rab<br>0 | Fon: set follower circuit on/off<br>Rab2~0:<br>select follower amplified ratio.                                   | 26.3 µs | 18.5 µs | 14.3 µs |

| Contrast Set                           | 0 | 0 | 0 | 1 | 1 | 1    | СЗ   | C2       | C1       | CO       | Contrast set for internal follower mode.                                                                          | 26.3 μs | 18.5 µs | 14.3 µs |

|                                        |   |   |   |   |   | Inst | truc | tior | ı ta | ble | 2(IS[2:1]=[1,0])                  |         |         |         |

|----------------------------------------|---|---|---|---|---|------|------|------|------|-----|-----------------------------------|---------|---------|---------|

| Double<br>Height<br>Position<br>Select | 0 | 0 | 0 | 0 | 0 | 1    | UD   | ×    | х    | х   | UD: Double height position select | 26.3 µs | 18.5 µs | 14.3 µs |

| Reserved                               | 0 | 0 | 0 | 1 | Х | Х    | Х    | X    | Х    | Х   | Do not use (reserved for test)    | 26.3 μs | 18.5 µs | 14.3 µs |

Instruction table 3(IS[2:1]=[1,1]):Do not use (reserved for test)

## 12.Standard character pattern

| 67-64<br>63-60 | 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 | 1000 | 1001 | 1010 | 1011 | 1100 | 1101 | 1110 | 1111 |

|----------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| 0000           |      |      |      |      |      |      |      |      |      |      |      |      |      | ***  |      |      |

| 0001           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 0010           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 0011           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 0100           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 0101           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 0110           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 0111           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 1000           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 1001           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 1010           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 1011           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 1100           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 1101           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 1110           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 1111           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

## CGRAM/CGROM arrangement with(OPR1=0;OPR2=0)

| (0,0)                              | (0,1)                 | (1,0)                 | (1,1)                          |

|------------------------------------|-----------------------|-----------------------|--------------------------------|

| 67-64<br>60-60<br>0000<br>0001<br> | 57-56 0000 0001 · · · | 60-60 0000 0001 · · · | 67-54<br>60-60 0000 0001 · · · |

| ··· 🖫 ···                          | 0000                  | 0000                  | occo 🖺 🖫 · · ·                 |

| ccc1                               | 0001                  | 0001                  | 0001 🗓 📅 …                     |

| 0010                               | 0010                  | 0010                  | 0010 🔯 🐯 …                     |

| 0011                               | 0011                  | 0011                  | 0011 🗗 📆 …                     |

| 0100                               | 0100                  | 0100                  | 0100 🛱 📙                       |

| 0101                               | 0101                  | 0101                  | 0101                           |

| 0410                               | 0110 🛄                | 0110                  | омо 👃 🗒                        |

| 0111                               | 0111                  | 0111                  | 0111 👺 👸                       |

| 1000                               | 1000                  | 1000 🗱 🗮              | 1000 🖶 🖪 …                     |

| 1001                               | 1001                  | 1001                  | 1001                           |

| 1010                               | 1010                  | 1010                  | 1010                           |

| 1011                               | 1011                  | 1011                  | 1011                           |

| 1100                               | 1100                  | 1100                  | 1100                           |

| 1101                               | 1101                  | 1101 🕱 🖳              | 1101                           |

| 1110                               | 1110 🖺 🖫              | 1110 🔯 🖫              | 1110 📓 🖫                       |

| 1111                               | 1111 📓 🔐              | 1111 🐯 🔯              | 1111 🔯 🔯                       |

### 13.QUALITY SPECIFICATIONS

## 13.1 Standard of the product appearance test

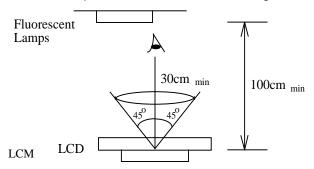

Manner of appearance test: The inspection should be performed in using 20W x 2 fluorescent lamps. Distance between LCM and fluorescent lamps should be 100 cm or more. Distance between LCM and inspector eyes should be 30 cm or more.

Viewing direction for inspection is 45° from vertical against LCM.

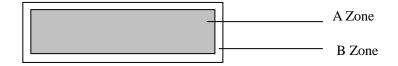

Definition of zone:

A Zone: Active display area (minimum viewing area).

B Zone: Non-active display area (outside viewing area).

# **13.2 Specification of quality assurance** AQL inspection standard

Sampling method: MIL-STD-105E, Level II, single sampling

Defect classification (Note: \* is not including)

| Classify |               | Item                         | Note | AQL  |

|----------|---------------|------------------------------|------|------|

| Major    | Display state | Short or open circuit        | 1    | 0.65 |

|          |               | LC leakage                   |      |      |

|          |               | Flickering                   |      |      |

|          |               | No display                   |      |      |

|          |               | Wrong viewing direction      |      |      |

|          |               | Contrast defect (dim, ghost) | 2    |      |

|          |               | Back-light                   | 1,8  |      |

|          | Non-display   | Flat cable or pin reverse    | 10   |      |

|          |               | Wrong or missing component   | 11   |      |

| Minor    | Display       | Background color deviation   | 2    | 1.0  |

|          | state         | Black spot and dust          | 3    |      |

|          |               | Line defect, Scratch         | 4    |      |

|          |               | Rainbow                      | 5    |      |

|          |               | Chip                         | 6    |      |

|          |               | Pin hole                     | 7    |      |

|          |               | Protruded                    | 12   |      |

|          | Polarizer     | Bubble and foreign material  | 3    |      |

|          | Soldering     | Poor connection              | 9    |      |

|          | Wire          | Poor connection              | 10   |      |

|          | TAB           | Position, Bonding strength   | 13   |      |

#### Note on defect classification

| No. | Item                              |                                       |       |      | Criterion                                            |                         |

|-----|-----------------------------------|---------------------------------------|-------|------|------------------------------------------------------|-------------------------|

| 1   | Short or open circuit             |                                       |       |      | Not allow                                            |                         |

|     | LC leakage                        |                                       |       |      |                                                      |                         |

|     | Flickering                        |                                       |       |      |                                                      |                         |

|     | No display                        |                                       |       |      |                                                      |                         |

|     | Wrong viewing direction           |                                       |       |      |                                                      |                         |

|     | Wrong Back-light                  |                                       |       |      |                                                      |                         |

| 2   | Contrast defect                   |                                       | Refe  | r to | approval sa                                          | mple                    |

|     | Background color deviation        |                                       |       |      |                                                      |                         |

| 3   | Point defect,<br>Black spot, dust | <b>Q</b> ↑Y                           |       |      | Point<br>Size                                        | Acceptable Qty.         |

|     | (including Polarizer)             | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |       |      | φ <u>&lt;</u> 0.10                                   | Disregard               |

|     |                                   |                                       |       |      | .10<φ≤0.20                                           | 3                       |

|     | $\phi = (X+Y)/2$                  |                                       |       |      | .20<φ≤0.25<br>.25<φ≤0.30                             | 2                       |

|     |                                   |                                       |       | 0    | φ>0.30                                               | Unit: mm                |

|     |                                   |                                       |       |      |                                                      | Office fillin           |

| 4   | Line defect,                      | _ ↓                                   |       |      |                                                      |                         |

| -   |                                   | <b>~</b> ™W                           |       |      | Line                                                 | Acceptable Qty.         |

|     | Scratch                           | $\leftrightarrow$                     | L     |      | W                                                    | D: 1                    |

|     |                                   | L                                     | 3.0≥  |      | 0.015≥W                                              | Disregard               |

|     |                                   |                                       | 2.0≥  |      | 0.03≥W<br>0.05≥W                                     | 2                       |

|     |                                   |                                       | 1.0>  |      | 0.03> W                                              | 1                       |

|     |                                   |                                       |       |      | 0.05 <w< td=""><td>Applied as point defect</td></w<> | Applied as point defect |

|     |                                   |                                       |       |      |                                                      | Unit: mm                |

| 5   | Rainbow                           | Not more than t                       | wo co | lor  | changes acr                                          | oss the viewing area.   |

| No | Item                                                                       | Criterion                                                                   |

|----|----------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| 6  | Chip  Remark: X: Length direction Y: Short direction                       | Acceptable criterion $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

|    | Z: Thickness<br>direction<br>t: Glass<br>thickness<br>W: Terminal<br>Width | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                       |

|    |                                                                            | Acceptable criterion $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ |

|    |                                                                            | Acceptable criterion $\begin{array}{c ccccccccccccccccccccccccccccccccccc$  |

|    |                                                                            | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                       |

| No. | Item                                          | Criterion                                                                                                                                                                                                                                      |

|-----|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Segment pattern W = Segment width φ = (X+Y)/2 | (1) Pin hole $\phi < 0.10 \text{mm is acceptable.}$ $Y$                                                                                                                                                    |

| 8   | Back-light                                    | <ul><li>(1) The color of backlight should correspond its specification.</li><li>(2) Not allow flickering</li></ul>                                                                                                                             |

| 9   | Soldering                                     | (1) Not allow heavy dirty and solder ball on PCB.  (The size of dirty refer to point and dust defect)  (2) Over 50% of lead should be soldered on Land.  Lead  Land  50% lead                                                                  |

| 10  | Wire                                          | <ul><li>(1) Copper wire should not be rusted</li><li>(2) Not allow crack on copper wire connection.</li><li>(3) Not allow reversing the position of the flat cable.</li><li>(4) Not allow exposed copper wire inside the flat cable.</li></ul> |

| 11* | PCB                                           | <ul><li>(1) Not allow screw rust or damage.</li><li>(2) Not allow missing or wrong putting of component.</li></ul>                                                                                                                             |

| No | ltem                           | Criterion                                                                                                                                                                                                           |  |  |

|----|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 12 | Protruded W: Terminal Width    | Acceptable criteria: $Y \le 0.4$                                                                                                                                                                                    |  |  |

| 13 | TAB                            | 1. Position $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                    |  |  |

| 14 | Total no. of acceptable Defect | A. Zone  Maximum 2 minor non-conformities per one unit.  Defect distance: each point to be separated over 10mm  B. Zone  It is acceptable when it is no trouble for quality and assembly in customer's end product. |  |  |

### 13.3 Reliability of LCM

Reliability test condition:

| Item                 | Condition                                                                                         | Time (hrs) | Assessment                                   |

|----------------------|---------------------------------------------------------------------------------------------------|------------|----------------------------------------------|

| High temp. Storage   | 80°C                                                                                              | 48         |                                              |

| High temp. Operating | 70°C                                                                                              | 48         | No abnormalities in functions and appearance |

| Low temp. Storage    | -30°C                                                                                             | 48         |                                              |

| Low temp. Operating  | -20°C                                                                                             | 48         |                                              |

| Humidity             | 40°C/ 90%RH                                                                                       | 48         |                                              |

| Temp. Cycle          | $0^{\circ}$ C ← $25^{\circ}$ C $\rightarrow 50^{\circ}$ C<br>(30 min ← 5 min $\rightarrow$ 30min) | 10cycles   |                                              |

Recovery time should be 24 hours minimum. Moreover, functions, performance and appearance shall be free from remarkable deterioration within 50,000 hours under ordinary operating and storage conditions room temperature (20±8°C), normal humidity (below 65% RH), and in the area not exposed to direct sun light.

### 13.4 Precaution for using LCD/LCM

LCD/LCM is assembled and adjusted with a high degree of precision. Do not attempt to make any alteration or modification. The followings should be noted.

#### **General Precautions:**

- 1. LCD panel is made of glass. Avoid excessive mechanical shock or applying strong pressure onto the surface of display area.

- 2. The polarizer used on the display surface is easily scratched and damaged. Extreme care should be taken when handling. To clean dust or dirt off the display surface, wipe gently with cotton, or other soft material soaked with isoproply alcohol, ethyl alcohol or trichlorotriflorothane, do not use water, ketone or aromatics and never scrub hard.

- 3. Do not tamper in any way with the tabs on the metal frame.

- 4. Do not make any modification on the PCB without consulting Focus Display Solutions, Inc.

- 5. When mounting a LCM, make sure that the PCB is not under any stress such as bending or twisting. Elastomer contacts are very delicate and missing pixels could result from slight dislocation of any of the elements.

- 6. Avoid pressing on the metal bezel, otherwise the elastomer connector could be deformed and lose contact, resulting in missing pixels and also cause rainbow on the display.

- 7. Be careful not to touch or swallow liquid crystal that might leak from a damaged cell. Any liquid crystal adheres to skin or clothes, wash it off immediately with soap and water.

#### **Static Electricity Precautions:**

- 1. CMOS-LSI is used for the module circuit; therefore operators should be grounded whenever he/she comes into contact with the module.

- 2. Do not touch any of the conductive parts such as the LSI pads; the copper leads on the PCB and the interface terminals with any parts of the human body.

- 3. Do not touch the connection terminals of the display with bare hand; it will cause disconnection or

- defective insulation of terminals.

- 4. The modules should be kept in anti-static bags or other containers resistant to static for storage.

- 5. Only properly grounded soldering irons should be used.

- 6. If an electric screwdriver is used, it should be grounded and shielded to prevent sparks.

- 7. The normal static prevention measures should be observed for work clothes and working benches.

- 8. Since dry air is inductive to static, a relative humidity of 50-60% is recommended.

### **Soldering Precautions:**

- 1. Soldering should be performed only on the I/O terminals.

- 2. Use soldering irons with proper grounding and no leakage.

- 3. Soldering temperature: 280°C±10°C

- 4. Soldering time: 3 to 4 second.

- 5. Use eutectic solder with resin flux filling.

- 6. If flux is used, the LCD surface should be protected to avoid spattering flux.

- 7. Flux residue should be removed.

#### **Operation Precautions:**

- 1. The viewing angle can be adjusted by varying the LCD driving voltage Vo.

- 2. Since applied DC voltage causes electro-chemical reactions, which deteriorate the display, the applied pulse waveform should be a symmetric waveform such that no DC component remains. Be sure to use the specified operating voltage.

- 3. Driving voltage should be kept within specified range; excess voltage will shorten display life.

- 4. Response time increases with decrease in temperature.

- 5. Display color may be affected at temperatures above its operational range.

- 6. Keep the temperature within the specified range usage and storage. Excessive temperature and humidity could cause polarization degradation, polarizer peel-off or generate bubbles.

- 7. For long-term storage over 40°C is required, the relative humidity should be kept below 60%, and avoid direct sunlight.