Ph. 480-503-4295 | NOPP@FocusLCD.com

# TFT | CHARACTER | UWVD | FSC | SEGMENT | CUSTOM | REPLACEMENT

# **TFT** Display Module

Part Number E35RB-FW115-N

## **Overview:**

- 3.5-inch TFT: 480x640 (64x85)

- 3 SPI+16/18- bit RGB

- White LED back-light

- Transflective/ Normally Black

- No Touch Panel

- 115 NITS

- Controller: HX8363-A

- RoHS Compliant

#### Description

This is a color active matrix TFT (Thin Film Transistor) LCD (Liquid Crystal Display) that uses amorphous silicon TFT as a switching device. This model is composed of a Transflective type TFT-LCD Panel, driver circuit, back-light unit. The resolution of a 3.5" TFT-LCD contains 480x640 pixels, and can display up to 65K/262K colors.

#### Features

Low Input Voltage: 3.3V (TYP) Display Colors of TFT LCD: 65K/262K colors TFT Interface: 3 SPI+16/18Bit RGB

| General Information   | Specification                 | – Unit  | Note |

|-----------------------|-------------------------------|---------|------|

| Items                 | Main Panel                    | Onit    | Note |

| Display area (AA)     | 53.57(H) *71.42(V) (3.5 inch) | mm      | -    |

| Driver element        | TFT active matrix             | -       | -    |

| Display colors        | 65K/262K                      | colors  | -    |

| Number of pixels      | 480(RGB)*640                  | dots    | -    |

| TFT Pixel arrangement | RGB vertical stripe           | -       | -    |

| Pixel pitch           | 0.135(H) x 0.135 (V)          | mm      | -    |

| Viewing angle         | Wide angle                    | o'clock | -    |

| TFT Controller IC     | HX8363-A                      | -       | -    |

| Display mode          | Transflective/Normally Black  | -       | -    |

| Operating temperature | -20~+70                       | °C      | -    |

| Storage temperature   | -30~+80                       | °C      | _    |

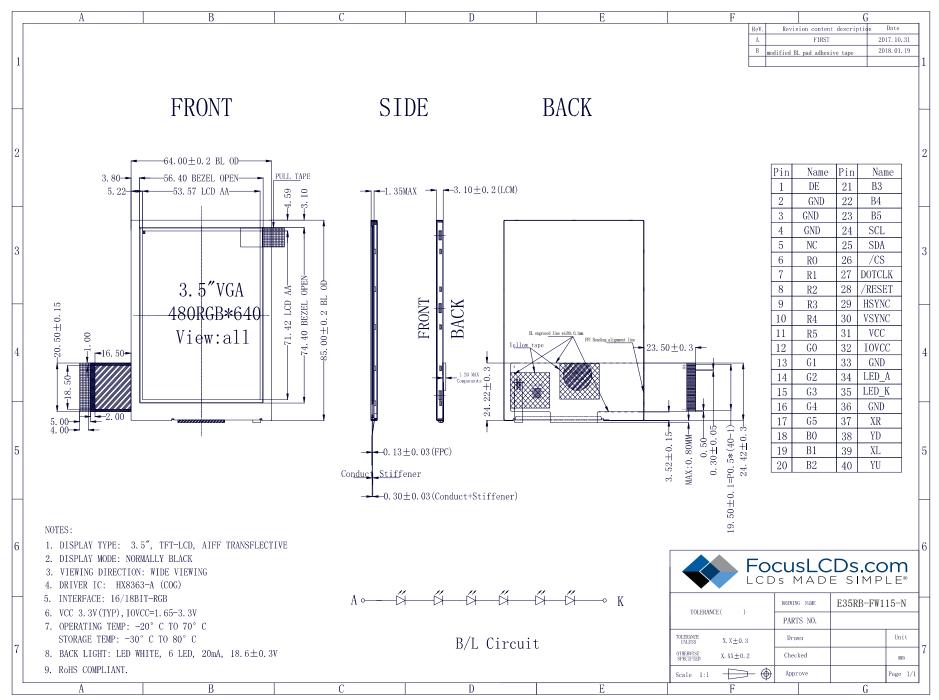

#### **Mechanical Information**

|                    | ltem          | Min | Тур. | Max | Unit | Note |

|--------------------|---------------|-----|------|-----|------|------|

| Module V<br>size V | Horizontal(H) |     | 64.0 |     | mm   | -    |

|                    | Vertical(V)   |     | 85.0 |     | mm   | -    |

|                    | Depth(D)      |     | 3.10 |     | mm   | -    |

|                    | Weight        |     | 34   |     | g    | -    |

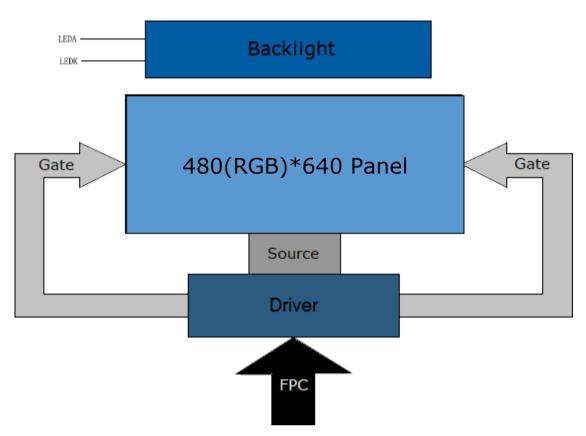

# 1. Block Diagram

### 2. Outline dimensions

# 3. Input Terminal Pin Assignment

Recommended Connector: FH19C-40S-0.5SH(10)

| NO.   | Symbol | Description                                                                                                                                                                  | I/O |

|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1     | DE     | Data enable signal in RGB I/F mode. Fixed to GND in MPU interface mode.                                                                                                      | Ι   |

| 2     | GND    | Ground                                                                                                                                                                       | Р   |

| 3     | GND    | Ground                                                                                                                                                                       | Р   |

| 4     | GND    | Ground                                                                                                                                                                       | Р   |

| 5     | NC     |                                                                                                                                                                              |     |

| 6-11  | R0-R5  | Red data bus                                                                                                                                                                 | I/O |

| 12-17 | G0-G5  | Green data bus                                                                                                                                                               | I/O |

| 18-23 | B0-B5  | Blue data bus                                                                                                                                                                | I/O |

| 24    | SCL    | Serves as a write signal and writes data at the rising edge. When operate in serial interface, it serves as SCL (Serial Clock). If not used, let it open or connected to VCC | I   |

| 25    | SDA    | Serial data input pin in serial interface operation                                                                                                                          | I   |

| 26    | CS     | Chip select input pin ("Low" enable). Fix this pin at VCI or GND when not in use.                                                                                            | Ι   |

| 27    | DOTCLK | Dot clock signal. Must be connected to GND or VCC if not used.                                                                                                               | I   |

| 28    | RESET  | Reset pin. Setting either pin low initializes the LSI. Must be reset after power is                                                                                          |     |

| 20    | RESET  | supplied (Must be connected to GND or VCC). (Latch type)                                                                                                                     | l.  |

| 29    | HSYNC  | Line synchronizing signal. Must be connected to GND or VCC if not used.                                                                                                      | I.  |

| 30    | VSYNC  | Frame synchronizing signal. Must be connected to GND or VCC if not used.                                                                                                     |     |

| 31    | VCC    | Supply voltage (3.3V)                                                                                                                                                        |     |

| 32    | IOVCC  | A power supply for the I/O circuit. (1.65-3.3V)                                                                                                                              | Ι   |

| 33    | GND    | Ground                                                                                                                                                                       | 0   |

| 34    | LED_A  | Anode pin of backlight                                                                                                                                                       | Р   |

| 35    | LED_K  | Cathode pin of backlight                                                                                                                                                     | Р   |

| 36    | GND    | Ground                                                                                                                                                                       | Р   |

| 37    | XR     | Touch panel right glass terminal                                                                                                                                             | A/D |

| 38    | YD     | Touch panel bottom film terminal                                                                                                                                             | A/D |

| 39    | XL     | Touch panel left glass terminal                                                                                                                                              | A/D |

| 40    | YU     | Touch panel top film terminal                                                                                                                                                | A/D |

# 4. LCD Optical Characteristics

# 4.1 Optical Specifications

| ltem                          |                       | Symbol         | Condition     | Min.  | Тур.  | Max.  | Unit. | Note   |

|-------------------------------|-----------------------|----------------|---------------|-------|-------|-------|-------|--------|

| Contrast Ratio                |                       | CR             | Θ=0           | 200   | 300   |       |       | (2)    |

| Reflection Rati<br>polarizer) | io (with              | R              | Normal        |       | 7     |       | %     | (3)    |

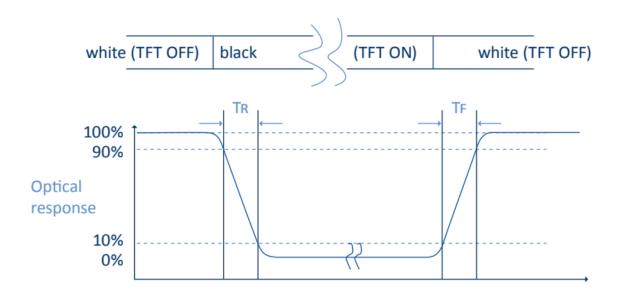

| Response<br>time              | Rising+<br>Falling    | TR+TF          | viewing angle |       | 30    | 50    | msec  | (4)    |

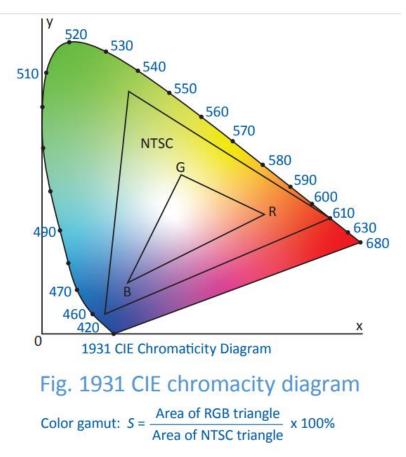

| Color gam                     | nut                   | S (%)          |               |       | 60    |       | %     | (5)    |

| White                         | Wx                    |                | 0.248         | 0.288 | 0.328 |       |       |        |

|                               | White                 | Wy             |               | 0.272 | 0.312 | 0.352 |       |        |

|                               | Red                   | Rx             |               | 0.425 | 0.465 | 0.505 |       |        |

| Color Filter                  | Red                   | Ry             |               | 0.286 | 0.326 | 0.366 |       | (5)(6) |

| Chromaticity                  | Green                 | Gx             |               | 0.277 | 0.317 | 0.357 |       |        |

|                               | Green                 | Gy             |               | 0.485 | 0.498 | 0.538 |       |        |

|                               | Blue                  | B <sub>x</sub> |               | 0.135 | 0.175 | 0.215 |       |        |

|                               | Blue                  | B <sub>Y</sub> |               | 0.075 | 0.115 | 0.115 |       |        |

|                               | Hor.                  | ΘL             |               | 60    | 80    |       |       |        |

| Viewing angle                 |                       | ΘR             |               | 60    | 80    |       |       | (1)    |

|                               | Ver.                  | ΘU             | CR>10         | 60    | 80    |       |       |        |

|                               |                       | ΘD             |               | 60    | 80    |       |       |        |

| Option View Di                | Option View Direction |                |               | ALL   |       |       |       |        |

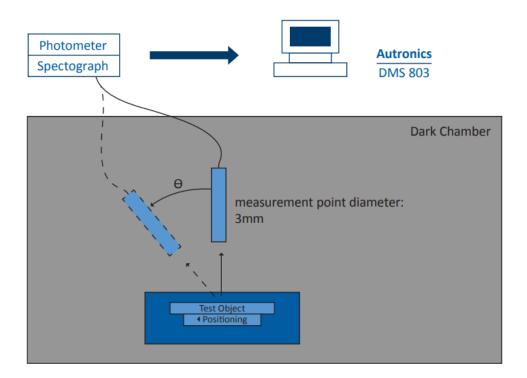

#### 4.2 Measuring Conditions

Measuring surrounding: dark room Ambient temperature: 25 ± 2°C 15min. warm-up time

#### **Optical Specification Reference Notes:**

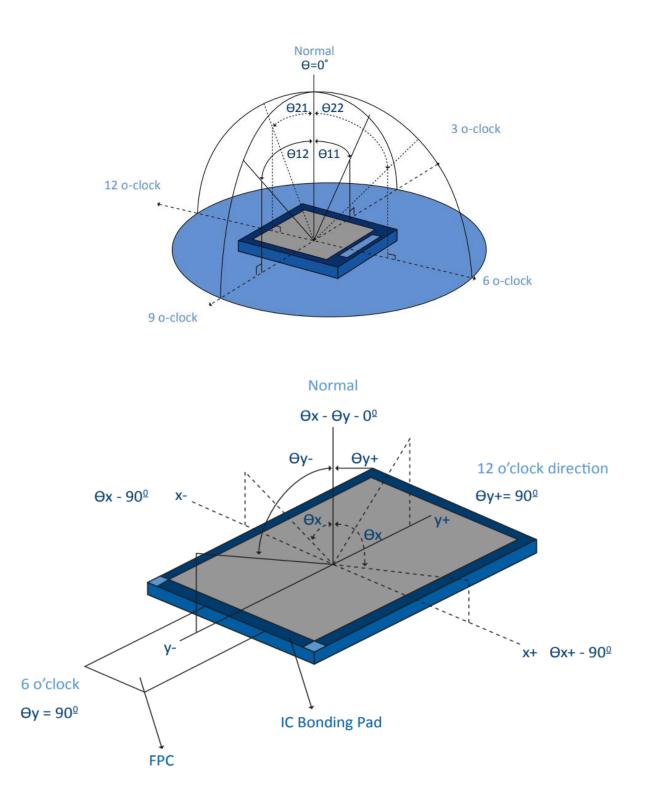

(1) Definition of Viewing Angle: The viewing angle is the angle at which the contrast ratio is greater than 10. The viewing angles are determined for the horizontal or 3,9 o'clock direction and the vertical or 6,12 o'clock direction with respect to the optical axis which is normal to the LCD surface.

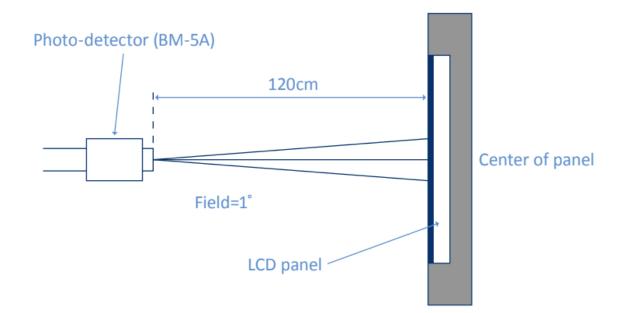

(2) Definition of Contrast Ratio (Cr): measured at the center point of panel. The contrast ratio (Cr) measured on a module, is the ratio between the luminance (Lw) in a full white area (R=G=B=1) and the luminance (Ld) in a dark area (R=G=B=0).

$$Cr = \frac{Lw}{Ld}$$

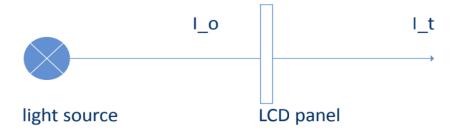

(3) Definition of transmittance (T%): The transmittance of the panel including the polarizers is measured with electrical driving.

The transmittance is defined as:

$$Tr = \frac{It}{Io} x \ 100\%$$

Io = the brightness of the light source.

It = the brightness after panel transmission

(4) Definition of Response Time (Tr, Tf): The rise time 'Tr' is defined as the time for luminance to change from 90% to 10% as a result of a change of the electrical condition. The fall time 'Tf' is defined as the time for luminance to change from 10% to 90% as a result of a change of the electrical condition.

(5) Definition of Color Gamut: Measuring machine CFT-01. NTSC's Primaries: R(x,y,Y),G(x,y,Y), B(x,y,Y). FPM520 of Westar Display Technologies, INC., which utilized SR-3 for Chromaticity and BM-5A for other optical characteristics.

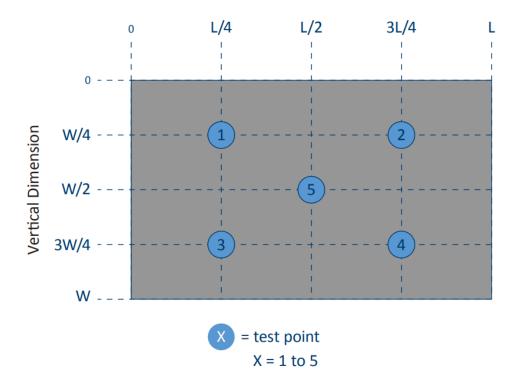

(6) Definition of Optical Measurement Setup:

(6) Optical Measurement Setup Continued:

The LCD module should be stabilized at a given temperature for 20 minutes to avoid abrupt temperature change during measuring. In order to stabilize the luminance, the measurement should be executed after lighting backlight for 20 minutes.

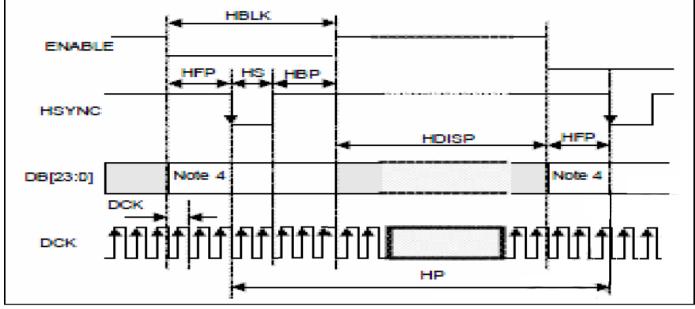

### **Horizontal Dimension**

### 5. Electrical Characteristics

# 5.1 Absolute Maximum Rating (Ta=25 VSS=0V)

| Characteristics             | Symbol | Min  | Max | Unit |

|-----------------------------|--------|------|-----|------|

| Digital Supply Voltage      | VCI    | -0.3 | 4.6 | V    |

| Interface Operation Voltage | IOVCC  | -0.3 | 4.6 | V    |

| Operating temperature       | ТОР    | -20  | +70 | °C   |

| Storage temperature         | TST    | -30  | +80 | °C   |

NOTE: If the absolute maximum rating of even is one of the above parameters is exceeded even momentarily, the quality of the product may be degraded. Absolute maximum ratings, therefore, specify the values exceeding which the product may be physically damaged. Be sure to use the product within the range of the absolute maximum ratings.

#### 5.2 DC Electrical Characteristics

| Characteristics                    | Symbol      | Min.      | Тур. | Max.      | Unit | Note |

|------------------------------------|-------------|-----------|------|-----------|------|------|

| Digital Supply Voltage             | VCI         | 2.5       | 3.3  | 3.6       | V    |      |

| Interface Operation<br>Voltage     | ΙΟΥϹϹ       | 1.65      | 1.8  | 3.3       | V    |      |

| Normal Mode Current<br>Consumption | IVCC+IIOVCC |           | 20   | 40        | mA   |      |

| Level input voltage                | VIH         | 0.7 IOVCC |      | IOVCC     | V    |      |

| Level input voitage                | VIL         | GND       |      | 0.3 IOVCC | V    |      |

| Level output voltage               | VOH         | 0.8 IOVCC |      | IOVCC     | V    |      |

| Level output voltage               | VOL         | GND       |      | 0.2 IOVCC | V    |      |

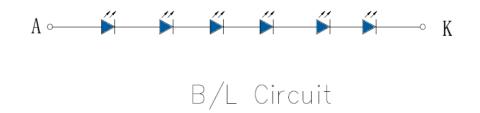

#### 5.3 LED Backlight Characteristics

| Item            | Symbol | Min   | Тур. | Max | Unit  | Note         |

|-----------------|--------|-------|------|-----|-------|--------------|

| Forward Current | IF     | 15    | 20   |     | mA    |              |

| Forward Voltage | VF     |       | 18.6 |     | V     |              |

| LCM Luminance   | LV     | 65    | 115  |     | cd/m2 | Note 3       |

| LED lifetime    | Hr     | 50000 |      |     | hour  | Note1<br>& 2 |

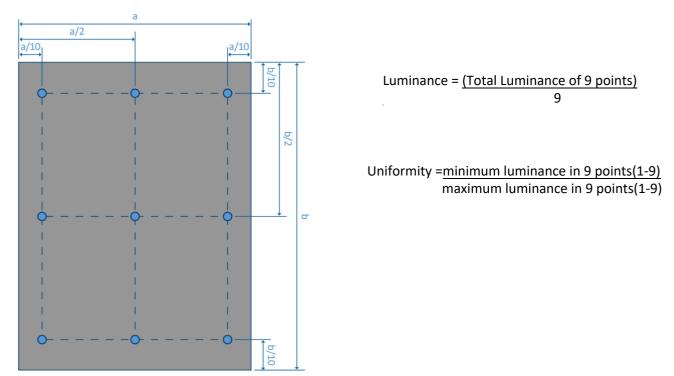

| Uniformity      | AVg    | 80    |      |     | %     | Note 3       |

The back-light system is edge-lighting type with 6 chips White LED

Note 1: LED lifetime (Hr) can be defined as the time in which it continues to operate under the condition: Ta=25  $\pm 3$  °C, typical IL value indicated in the above table until the brightness becomes less than 50%.

Note 2: The "LED lifetime" is defined as the module brightness decrease to 50% original brightness at Ta=25°C and IL=20mA. The LED lifetime could be decreased if operating IL is larger than 20mA. The constant current driving method is suggested.

#### Note 3: Luminance Uniformity of these 9 points is defined as below:

### 6. AC Characteristic

#### 6.1 RGB Interface Characteristics

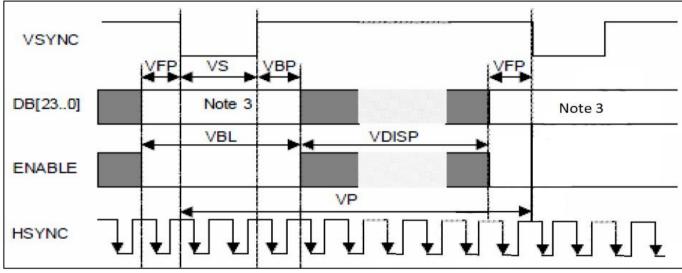

Vertical Timings for RGB I/F

#### Resolution=480x854, VSSA=VSSD=0V, VDD1=1.65V to 3.3V, VDD2=2.5 to 3.3V, VDD3=2.5 to 3.3V, TA= -30 to 70°C

| Item                      | Symbol | Condition  | Min | Тур. | Max | Unit |

|---------------------------|--------|------------|-----|------|-----|------|

| Vertical cycle            | VP     |            | 860 |      | 864 | Line |

| Vertical low pulse width  | VS     |            | 2   |      | 4   | Line |

| Vertical front porch      | VFP    |            | 2   |      | 4   | Line |

| Vertical back porch       | VBP    |            | 2   |      | 4   | Line |

| Vertical data start point | -      | VS+VBP     | 4   |      | 8   | Line |

| Vertical blanking period  | VBL    | VS+VBP+VFP | 6   |      | 10  | Line |

| Vertical active area      | -      | VDISP      |     | 854  |     | Line |

| Vertical refresh rate     | VRR    |            | 50  |      | 70  | Hz   |

Table 6.3: RGB Interface Vertical Timing Characteristics (Resolution 480x854)

Note:

- (1) Signal rise and fall times are equal to or less than 20ns.

- (2) Input signals are measured by 0.30 x VDD1 for low state and 0.70 x VDD1 for high state.

- (3) Data lines can be set to "high" or "low" during blanking time.

- (4) VRR must keep from 50Hz to 70Hz when adjusting other items.

Resolution=480x800, VSSA=VSSD=0V, VDD1=1.65V to 3.3V, VDD2=2.5 to 3.3V, VDD3=2.5 to 3.3V, TA= -30 to 70°C

| Item                      | Symbol | Condition  | Min | Тур. | Max | Unit |  |  |  |

|---------------------------|--------|------------|-----|------|-----|------|--|--|--|

| Vertical cycle            | VP     |            | 806 |      | 810 | Line |  |  |  |

| Vertical low pulse width  | VS     |            | 2   |      | 4   | Line |  |  |  |

| Vertical front porch      | VFP    |            | 2   |      | 4   | Line |  |  |  |

| Vertical back porch       | VBP    |            | 2   |      | 4   | Line |  |  |  |

| Vertical data start point | -      | VS+VBP     | 4   |      | 8   | Line |  |  |  |

| Vertical blanking period  | VBL    | VS+VBP+VFP | 6   |      | 10  | Line |  |  |  |

| Vertical active area      | -      | VDISP      |     | 800  |     | Line |  |  |  |

| Vertical refresh rate     | VRR    |            | 50  |      | 70  | Hz   |  |  |  |

Table 6.4: RGB Interface Vertical Timing Characteristics (Resolution 480x800)

Figure 6.2: RGB Interface Vertical Timing Diagram

#### Horizontal Timings for RGB I/F

Figure 6.3: RGB Interface Horizontal Timing Diagram

| Item                        | Symbol | Condition             | Min  | Тур. | Max  | Unit |

|-----------------------------|--------|-----------------------|------|------|------|------|

| HS cycle                    | HP     | Note 3                | 504  |      | 568  | DCK  |

| HS low pulse width          | HS     |                       | 5    |      | 78   | DCK  |

| Horizontal front porch      | HFP    |                       | 5    |      | 78   | DCK  |

| Horizontal back porch       | HBP    |                       | 5    |      | 78   | DCK  |

| Herizontal data start point | -      | HS+HBP                | 19   |      | 83   | DCK  |

| Horizontal data start point |        |                       | 700  |      |      | ns   |

| Horizontal blanking period  | HBLK   | HS+HBP+HFP            | 24   |      | 88   | DCK  |

| Horizontal active area      | HDISP  |                       |      | 854  |      | DCK  |

| Pixel clock frequency       | DCK    | VRR=min 50Hz-max 70Hz | 21.6 |      | 34.3 | MHz  |

| when RGB I/F is runnig      | DCK    |                       | 29.1 |      | 46.2 | Ns   |

Table 6.5: RGB Interface Horizontal Timing Characteristics (Resolution 480x854)

Note:

(1) Signal rise and fall times are equal to or less than 20ns.

- (2) Input signals are measured by 0.30 x VDD1 for low state and 0.70 x VDD1 for high state.

- (3) Data lines can be set to "high" or "low" during blanking time.

- (4) VRR must keep from 50Hz to 70Hz when adjusting other items.

Resolution=480x800, VSSA=VSSD=0V, VDD1=1.65V to 3.3V, VDD2=2.5 to 3.3V, VDD3=2.5 to 3.3V, TA= -30 to 70°C

| ltem                        | Symbol | Condition             | Min  | Тур. | Max  | Unit |

|-----------------------------|--------|-----------------------|------|------|------|------|

| HS cycle                    | HP     | Note 3                | 504  |      | 568  | DCK  |

| HS low pulse width          | HS     |                       | 5    |      | 78   | DCK  |

| Horizontal front porch      | HFP    |                       | 5    |      | 78   | DCK  |

| Horizontal back porch       | HBP    |                       | 5    |      | 78   | DCK  |

| Uprizontal data start point | -      | - HS+HBP -            | 19   |      | 83   | DCK  |

| Horizontal data start point |        |                       | 700  |      |      | ns   |

| Horizontal blanking period  | HBLK   | HS+HBP+HFP            | 24   |      | 88   | DCK  |

| Horizontal active area      | HDISP  |                       |      | 854  |      | DCK  |

| Pixel clock frequency       | DCK    | VRR=min 50Hz-max 70Hz | 20.3 |      | 32.2 | MHz  |

| when RGB I/F is runnig      | DCK    |                       | 31   |      | 49.2 | Ns   |

Table 6.6: RGB Interface Horizontal Timing Characteristics (Resolution 480x854)

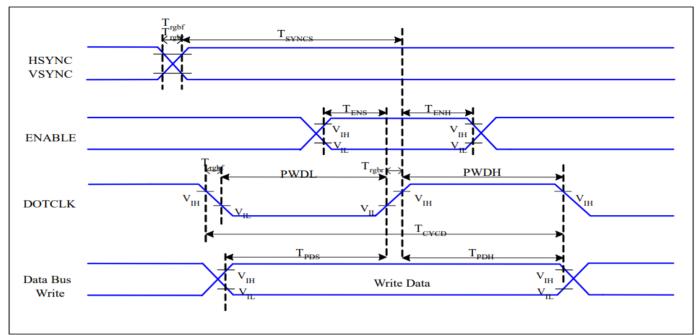

#### General timings for RGB I/F:

Figure 6.4: RGB Interface General Timing Diagram

#### Resolution=480x854, VSSA=VSSD=0V, VDD1=1.65V to 3.3V, VDD2=2.5 to 3.3V, VDD3=2.5 to 3.3V, TA= -30 to 70°C

| Item                                         | Symbol | Condition                | Min         | Тур. | Max         | Unit |

|----------------------------------------------|--------|--------------------------|-------------|------|-------------|------|

| Vertical sync setup time                     | VSST   |                          | 5           |      |             | ns   |

| Vertical sync hold time                      | VSHT   |                          | 5           |      |             | ns   |

| Horizontal sync setup time                   | HSST   |                          | 5           |      |             | ns   |

| Horizontal sync hold time                    | HSHT   |                          | 5           |      |             | ns   |

| Pixel clock cycle when RGB<br>I/F is running | DCKCYC | VRR = min 50Hz, max 70Hz | 29.1<br>(3) |      | 46.2<br>(4) | ns   |

| Pixel clock low time                         | DCKLT  |                          | 5           |      |             | ns   |

| Pixel clock high time                        | DCKHT  |                          | 5           |      |             | ns   |

| Data setup time DB[23:0]                     | DST    |                          | 5           |      |             | ns   |

| Data hold time DB[23:0]                      | DHT    |                          | 5           |      |             | ns   |

Table 6.7: RGB Interface General Timing Characteristics (Resolution 480x854)

Note:

(1) Signal rise and fall times are equal to or less than 20ns.

(2) Input signals are measured by 0.30 x VDD1 for low state and 0.70 x VDD1 for high state.

(3) 34.3 MHz

(4) 21.6 MHz

Resolution=480x800, VSSA=VSSD=0V, VDD1=1.65V to 3.3V, VDD2=2.5 to 3.3V, VDD3=2.5 to 3.3V, TA= -30 to 70°C

| ltem                       | Symbol | Condition                | Min  | Тур. | Max  | Unit |

|----------------------------|--------|--------------------------|------|------|------|------|

| Vertical sync setup time   | VSST   |                          | 5    |      |      | ns   |

| Vertical sync hold time    | VSHT   |                          | 5    |      |      | ns   |

| Horizontal sync setup time | HSST   |                          | 5    |      |      | ns   |

| Horizontal sync hold time  | HSHT   |                          | 5    |      |      | ns   |

| Pixel clock cycle when RGB | DCKCYC |                          | 31   |      | 49.2 | ns   |

| I/F is running             | DURCIU | VRR = min 50Hz, max 70Hz | 32.2 |      | 20.3 | MHz  |

| Pixel clock low time       | DCKLT  |                          | 5    |      |      | ns   |

| Pixel clock high time      | DCKHT  |                          | 5    |      |      | ns   |

| Data setup time DB[23:0]   | DST    |                          | 5    |      |      | ns   |

| Data hold time DB[23:0]    | DHT    |                          | 5    |      |      | ns   |

Table 6.8: RGB Interface General Timing Characteristics (Resolution 480x854)

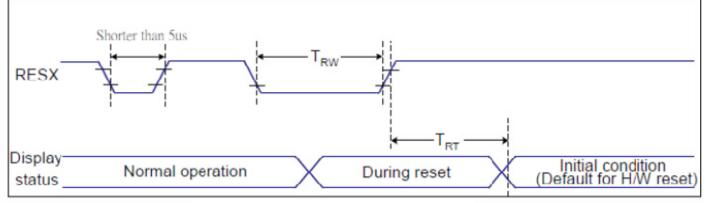

#### 6.2 Reset Timing

#### Figure 6.5: Reset Timing Diagram

| Related Pins | Symbol        | Parameter            | Min          | Max                | Unit |

|--------------|---------------|----------------------|--------------|--------------------|------|

|              | TRW           | Reset pulse duration | 10           | -                  | us   |

| RESX TRT     | Decet control | -                    | 5 (Note 1,5) | ms                 |      |

|              | IRI           | Reset cancel         |              | 120 (Note 1, 6, 7) | ms   |

Notes:

- 1. The reset cancel includes also required time for loading ID bytes, VCOM setting and other settings from NVM (or similar device) to registers. This loading is done every time when there is HW reset cancel time (tRT) within 5ms after a rising edge of RESX.

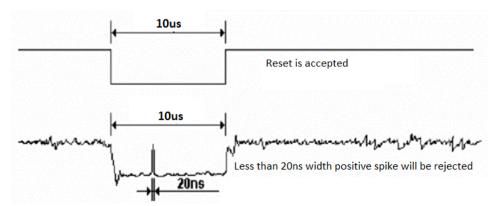

- 2. Spike due to an electrostatic discharge on RESX line does not because irregular system reset according to the table below:

| RESX Pulse           | Action         |

|----------------------|----------------|

| Shorter than 5us     | Reset Rejected |

| Longer than 9us      | Reset          |

| Between 5us and 9 us | Reset starts   |

- 3. During the resetting period, the display will be blanked (the display is entering blanking sequence, which maximum time is 120ms, when reset starts in Sleep Out mode. The display remains the blank state in Sleep in mode) and then return to Default condition for Hardware Reset.

- 4. Spike Rejection also applies during a valid reset pulse as shown below:

- 5. When Reset applied during Sleep In Mode.

- 6. When Reset applied during Sleep Out Mode.

- 7. It is necessary to wait 5ms after releasing RESX before sending commands. Also Sleep Out command cannot be sent for 120ms.

# 7. Cautions and Handling Precautions

# 7.1 Handling and Operating the Module

- 1. When the module is assembled, it should be attached to the system firmly. Do not warp or twist the module during assembly work.

- 2. Protect the module from physical shock or any force. In addition to damage, this may cause improper operation or damage to the module and back-light unit.

- 3. Note that polarizer is very fragile and could be easily damaged. Do not press or scratch the surface.

- 4. Do not allow drops of water or chemicals to remain on the display surface. If you have the droplets for a long time, staining and discoloration may occur.

- 5. If the surface of the polarizer is dirty, clean it using some absorbent cotton or soft cloth.

- 6. The desirable cleaners are water, IPA (Isopropyl Alcohol) or Hexane. Do not use ketene type materials (ex. Acetone), Ethyl alcohol, Toluene, Ethyl acid or Methyl chloride. It might permanent damage to the polarizer due to chemical reaction.

- 7. If the liquid crystal material leaks from the panel, it should be kept away from the eyes or mouth. In case of contact with hands, legs, or clothes, it must be washed away thoroughly with soap.

- 8. Protect the module from static; it may cause damage to the CMOS ICs.

- 9. Use fingerstalls with soft gloves in order to keep display clean during the incoming inspection and assembly process.

- 10. Do not disassemble the module.

- 11. Protection film for polarizer on the module shall be slowly peeled off just before use so that the electrostatic charge can be minimized.

- 12. Pins of I/F connector shall not be touched directly with bare hands.

- 13. Do not connect, disconnect the module in the "Power ON" condition.

- 14. Power supply should always be turned on/off by the item Power On Sequence & Power Off Sequence

## 7.2 Storage and Transportation

- 1. Do not leave the panel in high temperature, and high humidity for a long time. It is highly recommended to store the module with temperature from 0 to 35 °C and relative humidity of less than 70%

- 2. Do not store the TFT-LCD module in direct sunlight.

- 3. The module shall be stored in a dark place. When storing the modules for a long time, be sure to adopt effective measures for protecting the modules from strong ultraviolet radiation, sunlight, or fluorescent light.

- 4. It is recommended that the modules should be stored under a condition where no condensation is allowed. Formation of dewdrops may cause an abnormal operation or a failure of the module. In particular, the greatest possible care should be taken to prevent any module from being operated where condensation has occurred inside.

- 5. This panel has its circuitry FPC on the bottom side and should be handled carefully in order not to be stressed.